# NUMERICAL ANALYSIS DURING ENCAPSULATION PROCESS OF MOLDED UNDERFILL WITH MULTI FLIP CHIP PACKAGE

#### **MUHAMMAD AFIQ BIN AZMI**

UNIVERSITI SAINS MALAYSIA 2018

### NUMERICAL ANALYSIS DURING ENCAPSULATION PROCESS OF MOLDED UNDERFILL WITH MULTI FLIP CHIP PACKAGE

by

MUHAMMAD AFIQ BIN AZMI

Thesis submitted in fulfilment of the requirement for the Degree of

Master of Science

#### ACKNOWLEDGMENT

Alhamdulillah, all praises to Allah for the strength and His blessings for me to complete this thesis. Firstly, i would like to thank to the School of Material and Mineral Resources Engineering, Universiti Sains Malaysia (USM) led by Our Present Dean, Prof. Dr. Zuhailawati Binti Hussain for the giving me a great opportunities to extent my knowledge related to Polymer Engineering.

Secondly, a special thank goes to my supervisor, Ir. Dr. Muhammad Khalil Bin Abdullah @ Harun, my co-supervisors Ir. Prof. Dr. Mohd Zulkifly Bin Abdullah and Prof. Dr. Zulkifli Bin Mohamad Ariff for the supervision and support that they gave which is truly help the progression and smoothness of my study.

Thanks to Puan Hasnah and all support staff from School of Material and Mineral Resources Engineering and my colleagues Mr. Syakirin, Mr. Hafiz, Dr. Sharizal, Mr. Latif and Mr. Shawal that provide valuable information, suggestions, moral support and advice in dealing with life as a graduate student. I would like also to thanks CREST (304/PMEKANIK/6050299), Ministry of Education, Malaysia and School of Material and Mineral Resources Engineering short grant (304/PBAHAN/60313030) for the financial support throughout my studies.

Thanks for the wonderful love given by my parents who always believed in my ability. My child, Marwa Atifa and Muhammad Atif for the strength to continue to succeed in life and lastly deepest thanks and appreciation to my beloved wife, Noor Syazwani Binti Mansor that always there in good and bad times through life.

Thank you.

Muhammad Afiq Bin Azmi

#### TABLE OF CONTENTS

|     |                                                  | Page |

|-----|--------------------------------------------------|------|

| ACl | KNOWLEDGMENT                                     | ii   |

| TAI | BLE OF CONTENTS                                  | iii  |

| LIS | T OF TABLES                                      | iv   |

| LIS | T OF FIGURES                                     | v    |

| LIS | T OF ABBREVIATIONS                               | ix   |

| LIS | T OF SYMBOLS                                     | xi   |

|     | STRAK                                            | xiii |

| ABS | STRACT                                           | XV   |

| CH  | APTER ONE : INTRODUCTION                         |      |

| 1.1 | Overview of Integrated Circuit Packaging         | 1    |

| 1.2 | Molded Underfill of Flip Chip Package            | 4    |

| 1.3 | Numerical Analysis                               | 6    |

| 1.4 | Problem Statement and Challenges                 | 7    |

| 1.5 | Aim and Objectives                               | 8    |

| 1.6 | Scope of the Study                               | 8    |

| 1.7 | Thesis Outline                                   | 9    |

| CH  | APTER TWO : LITERATURE REVIEW                    |      |

| 2.1 | Integrated Circuit Encapsulation                 | 10   |

|     | 2.1.1 Capillary Underfill                        | 12   |

|     | 2.1.2 Pressurize Underfill                       | 13   |

|     | 2.1.3 No-flow Underfill                          | 14   |

|     | 2.1.4 Molded Underfill                           | 15   |

| 2.2 | Molded Underfill of Flip Chip Package Technology | 15   |

| 2.3 | Rheolog                                  | gy of Epoxy Molding Compound      | 17 |

|-----|------------------------------------------|-----------------------------------|----|

|     | 2.3.1                                    | Power Law Model                   | 19 |

|     | 2.3.2                                    | Cross Model                       | 20 |

|     | 2.3.3                                    | Castro Macosko Model              | 21 |

| 2.4 | Comput                                   | tational Simulation               | 24 |

| 2.5 | Summa                                    | ry                                | 26 |

| CII |                                          |                                   |    |

| CHA | APTER                                    | THREE: METHODOLOGY                |    |

| 3.1 | Introduc                                 | ction                             | 28 |

| 3.2 | Numeri                                   | cal Method                        | 30 |

|     | 3.2.1                                    | Rheological Model                 | 31 |

| 3.3 | Simulat                                  | cion Model and Boundary Condition | 33 |

|     | 3.3.1                                    | Volume of Fluid Tracking          | 36 |

|     | 3.3.2                                    | Boundary Condition                | 36 |

|     | 3.3.3                                    | Measuring Data                    | 37 |

| 3.4 | Mesh m                                   | nodeling and development          | 39 |

|     | 3.4.1                                    | Grid Dependency Test              | 40 |

| 3.5 | Validati                                 | ion Setup                         | 41 |

|     | 3.5.1                                    | Experimental Setup                | 41 |

|     | 3.5.2                                    | Simulation Setup                  | 44 |

| 3.6 | Summa                                    | ry                                | 45 |

|     |                                          |                                   |    |

| CHA | APTER I                                  | FOUR : RESULTS AND DISCUSSION     |    |

| 4.1 | Overvie                                  | ew                                | 46 |

| 4.2 | Experimental and Simulation Validation 4 |                                   |    |

| 4.3   | Encapsu  | ulation Process in Package and Single Multi Flip Chip Package | 50  |

|-------|----------|---------------------------------------------------------------|-----|

|       | 4.3.1    | Flow Front Visualization                                      | 51  |

|       | 4.3.2    | Velocity Profile Distribution                                 | 54  |

|       | 4.3.3    | Viscosity versus Shear Rate                                   | 56  |

|       | 4.3.4    | EMC behavior in Single Flip Chip Package                      | 57  |

|       | 4.3.5    | Void Formation                                                | 61  |

| 4.4   | Rheolog  | gical Effect during Encapsulation of Multi Flip Chip Packages | 63  |

|       | 4.4.1    | Flow Front Visualization                                      | 63  |

|       | 4.4.2    | Velocity, Shear Rate and Viscosity Profile                    | 66  |

|       | 4.4.3    | Viscosity versus Shear Rate                                   | 70  |

|       | 4.4.4    | Castro Macosko Model                                          | 71  |

|       | 4.4.5    | Void Formation                                                | 78  |

|       | 4.4.6    | Prediction of Curing Layer of EMC in the Cavity               | 80  |

| 4.5   | Effect o | of Stacking Design of Multi Flip Chips                        | 84  |

| 4.5.1 | Flow Fr  | cont Visualization                                            | 84  |

|       | 4.5.2    | Velocity, Shear Rate and Viscosity Profile                    | 87  |

|       | 4.5.3    | Viscosity versus Shear Rate                                   | 90  |

|       | 4.5.4    | Void Formation                                                | 91  |

|       | 4.5.5    | Cross Section of Flow Visualization                           | 94  |

| 4.6   | Rheolog  | gical Effect in Stacked Multi Flip Chips Package              | 95  |

|       | 4.6.1    | Flow Front Visualization                                      | 95  |

|       | 4.6.2    | Velocity, Shear Rate and Viscosity Profile                    | 99  |

|       | 4.6.3    | Formation of Weld Line Prediction at Solder Bump              | 102 |

| 17    | Summa    | PT.                                                           | 107 |

#### **CHAPTER FIVE: CONCLUSIONS**

| 5.1 | Conclusions                      | 108 |

|-----|----------------------------------|-----|

| 5.2 | Recommendations for Future Works | 110 |

REFERENCES 111

#### **APPENDICES**

Appendix A: Cross rhelogy data of polypropene LyondellBasell 6331 (LB6331) at 200°C from GÖTTFERT Rheograph25.

Appendix B: System Pressure Graph use in Injection Molding Machine Battenfeld TM750/210

#### LIST OF PUBLICATIONS

#### LIST OF TABLES

|            |                                              | Page |

|------------|----------------------------------------------|------|

| Table 3.1: | Geometry of Flip Chip Package                | 35   |

| Table 3.2: | Hitachi CEL-9200 XU (LF) material properties | 37   |

| Table 3.3: | The result of grid dependency test           | 41   |

#### LIST OF FIGURES

|              |                                                                                                                                   | Page |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1:  | Comparison of Cross model and Castro Macosko model flow front (Abdullah et al., 2009)                                             | 22   |

| Figure 2.2:  | Void position at MUF of flip chip package (Khor et al., 2012)                                                                     | 23   |

| Figure 2.3:  | Comparison of experiment data with model predictions at different temperatures of filling stage for RTM process (Lee & Wei, 2000) | 24   |

| Figure 3.1:  | Flow chart diagram of overview research study                                                                                     | 29   |

| Figure 3.2:  | Package Cavity with Multi Flip Chip Package                                                                                       | 34   |

| Figure 3.3:  | Package Cavity and its dimensions (unit: mm)                                                                                      | 34   |

| Figure 3.4:  | Flip Chip Package                                                                                                                 | 35   |

| Figure 3.5:  | Solder Bump with dimensions (unit: mm)                                                                                            | 35   |

| Table 3.1:   | Geometry of Flip Chip Package                                                                                                     | 35   |

| Table 3.2:   | Hitachi CEL-9200 XU (LF) material properties                                                                                      | 37   |

| Figure 3.6:  | (a) Isometric view (b) Side view of point surface inside the cavity                                                               | 38   |

| Figure 3.7:  | (a) Isometric view (b) Side view of line surface inside the cavity                                                                | 38   |

| Figure 3.8:  | Meshed model for Cavity Package                                                                                                   | 39   |

| Figure 3.9:  | Meshed model for Flip Chip Package                                                                                                | 39   |

| Figure 3.10: | Rheograph 25 Capillary Rheometer Machine GÖTTFERT                                                                                 | 42   |

| Figure 3.11: | Injection Molding Machine TM750/210                                                                                               | 43   |

| Figure 3.12: | Complete injected container                                                                                                       | 43   |

| Figure 3.13: | Container model with dimensions (unit: mm)                                                                                        | 44   |

| Figure 3.14: | Container meshed model                                                                                                            | 45   |

| Figure 4.1:  | Experimental and simulation flow front profiles of container for 10 MPa inlet pressure        | 48 |

|--------------|-----------------------------------------------------------------------------------------------|----|

| Figure 4.2:  | Flow front displacement at different time for 10 MPa                                          | 49 |

| Figure 4.3:  | Viscosity versus shear rate of cross model material between experiment and simulation results | 50 |

| Figure 4.4:  | Flow front profiles for empty package                                                         | 52 |

| Figure 4.5:  | Flow front profiles for multi flip chip packages                                              | 53 |

| Figure 4.6:  | Velocity profile distribution of EMC in empty cavity package                                  | 55 |

| Figure 4.7:  | Velocity profile distribution of EMC in multi flip chip package                               | 56 |

| Figure 4.8:  | Viscosity versus shear rate of EMC between empty cavity and multi flip chip package           | 57 |

| Figure 4.9:  | Temperature versus filling time of EMC in Single Flip Chip                                    | 58 |

| Figure 4.10: | Velocity versus filling time of EMC in Single Flip<br>Chip                                    | 59 |

| Figure 4.11: | Shear rate versus filling time of EMC in Single Flip Chip                                     | 60 |

| Figure 4.12: | Viscosity versus filling time of EMC in Single Flip<br>Chip                                   | 61 |

| Figure 4.13: | Void formation in molded underfill of flip chip package (in %)                                | 62 |

| Figure 4.14: | Percentage average volume of void formation in flip chip package                              | 63 |

| Figure 4.15: | Flow visualization of MUF package for different rheology models during encapsulation          | 65 |

| Figure 4.16: | Flow front displacement of all rheology model                                                 | 66 |

| Figure 4.17: | Velocity versus Z-direction of Cavity Package                                                 | 67 |

| Figure 4.18: | Shear rate versus Z-direction of Cavity Package                                               | 68 |

| Figure 4.19: | Viscosity versus Z-direction of Cavity Package                                                | 69 |

| Figure 4.20: | wiscosity versus shear rate for three different rheology models                              | 71 |

|--------------|----------------------------------------------------------------------------------------------|----|

| Figure 4.21: | Flow front in MUF for multi flip chip package using Castro Macosko Model                     | 73 |

| Figure 4.22: | EMC flow front displacement at different filling time for Castro Macosko model               | 74 |

| Figure 4.23: | Velocity versus Z-direction of Cavity Package                                                | 75 |

| Figure 4.24: | Sehar rate versus Z-direction of Cavity Package                                              | 76 |

| Figure 4.25: | Viscosity versus Z-direction of Cavity Package                                               | 77 |

| Figure 4.26: | Viscosity versus Shear rate of Castro Macosko model                                          | 78 |

| Figure 4.27: | Void formation at flip chip package (in %)                                                   | 79 |

| Figure 4.28: | Percentage average volume of void formation in three different row for Castro Macosko models | 80 |

| Figure 4.29: | Velocity profile of EMC in cavity package at different filling Time                          | 81 |

| Figure 4.30: | Temperature contour of EMC in cavity package during Encapsulation                            | 82 |

| Figure 4.31: | Velocity profile of EMC in single flip chip package at different filling time                | 83 |

| Figure 4.32: | Temperature contour of EMC in single flip chip package during encapsulation                  | 84 |

| Figure 4.33: | Flow visualization of various design of flip chip package during encapsulation process       | 86 |

| Figure 4.34: | Flow front displacement between different stacking of flip chip package during encapsulation | 87 |

| Figure 4.35: | Velocity versus Z-direction of cavity package in different stacking of flip chip package     | 88 |

| Figure 4.36: | Shear rate versus Z-direction of cavity package in different stacking of flip chip package   | 89 |

| Figure 4.37: | Viscosity versus Z-direction of cavity package in different stacking of flip chip package    | 90 |

| Figure 4.38: | Viscosity versus shear rate for various design of flip chip package during encapsulation                      | 91  |

|--------------|---------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.39: | Void formation for various design of flip chip package                                                        | 92  |

| Figure 4.40: | Percentage of void formation in three different design of flip chip package                                   | 93  |

| Figure 4.41: | Cross sectional flow visualization of various flip chip design during encapsulation                           | 95  |

| Figure 4.42: | Flow visualization of MUF flip chip package due to rheological effect (a) $\alpha=0.01$ and (b) $\alpha=0.05$ | 98  |

| Figure 4.43: | EMC flow front length with different rheological effect in various flip chip package design                   | 99  |

| Figure 4.44: | Velocity versus Z-direction of cavity package with different degree of conversion                             | 100 |

| Figure 4.45: | Shear rate versus Z-direction of cavity package with different degree of conversion                           | 101 |

| Figure 4.46: | Viscosity versus Z-direction of cavity cackage with different degree of conversion                            | 102 |

| Figure 4.47: | Schematic diagram of EMC flow inside the multi flip chip package                                              | 103 |

| Figure 4.48: | Flow visualization of EMC at solder bump of flip chip package during encapsulation                            | 105 |

| Figure 4.49: | First Collison Point and Merging Angle position in weld line prediction formation                             | 106 |

#### LIST OF ABBREVIATIONS

|       |                                    | Page |

|-------|------------------------------------|------|

| IC    | Integrated Circuit                 | xiii |

| CSP   | Chip Scale Package                 | xiii |

| MUF   | Molded Underfill                   | xiii |

| VOF   | Volume of Fluid                    | xiii |

| EMC   | Epoxy Molding Comppound            | xiii |

| THM   | Through-Hole Mount package         | 1    |

| SMT   | Surface Mount Package              | 1    |

| FCBGA | Flip Chip Ball Grid Arrays         | 2    |

| WBGA  | Wire Bond Ball Grid Arrays         | 2    |

| CUF   | Capillary Underfill                | 3    |

| NUF   | No-flow Underfill                  | 3    |

| CAE   | Computer-Aided Engineering         | 6    |

| FEA   | Finite Element Analysis            | 6    |

| CFD   | Computational Fluid Dynamics       | 6    |

| MBD   | Multibody Dynamics                 | 6    |

| FDM   | Finite Different Method            | 6    |

| FEM   | Finite Element Method              | 6    |

| FVM   | Finite Volume Method               | 6    |

| TQFP  | Thin Quad Flat Package             | 10   |

| TSOP  | Thin Profile Small Outline Package | 10   |

| MAP   | Mold array Package               | 10  |

|-------|----------------------------------|-----|

| S-CSP | Stacked-Chip Scale Package       | 10  |

| СТЕ   | Coefficient of Thermal Expansion | 11  |

| PUF   | Pressurize Underfill             | 12  |

| GNF   | Generalized Newtonian Fluid      | 18  |

| ICM   | Injection Compression Molding    | 20  |

| CIM   | Conventioanal Injection Molding  | 20  |

| EWLP  | Embedded Wafer Level Package     | 20  |

| PBGA  | Plastic Ball Grid Array          | 21  |

| TSV   | Through Silicon Via              | 21  |

| FSI   | Fluid/Structure Interaction      | 22  |

| DMA   | Dynamic Mechanical Analysis      | 23  |

| RTM   | Resin Transfer Molding           | 23  |

| CAD   | Computer Assisted Design         | 24  |

| PP    | Polypropene                      | 28  |

| FCR   | Flip Chip Region                 | 64  |

| FPR   | Flip Passage Region              | 64  |

| FCP   | First Collision Point            | 102 |

#### LIST OF SYMBOLS

| $T_g$       | Glass transition temperature            |

|-------------|-----------------------------------------|

| V           | Velocity vector                         |

| и           | Fluid velocity component in x-direction |

| v           | Fluid velocity component in y-direction |

| W           | Fluid velocity component in z-direction |

| P           | Pressure                                |

| T           | Temperature                             |

| $c_p$       | Specific Heat                           |

| k           | Thermal Conductivity                    |

| $\Delta H$  | Exothermic heat                         |

| K           | Flow consistency index                  |

| n           | Power Law index                         |

| В           | Exponential fitted constant             |

| $T_b$       | Temperature fitted constant             |

| $c_1$       | Fitting Constant                        |

| $c_2$       | Fitting Constant                        |

| F           | Front advancement parameter             |

| $T_{ m m}$  | Mold Temperature                        |

| $T_{ m in}$ | Temperature at inlet                    |

| (x, y, z)   | Cartesian coordinates                   |

| ρ            | Density                                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------------------|

| η            | Viscosity                                                                                                            |

| Ϋ            | Shear rate                                                                                                           |

| $\dot{lpha}$ | Conversion rate                                                                                                      |

| $\eta_o$     | Zero shear rate viscosity                                                                                            |

| $	au^*$      | A parameter that describes the transition region between power law region and zero shear rate of the viscosity curve |

| α            | Degree of Conversion                                                                                                 |

## ANALISIS BERANGKA SEMASA PROSES PENGKAPSULAN DALAM ACUAN ISIAN BAWAH DENGAN PEMPAKEJAN FLIP CIP BERGANDA

#### **ABSTRAK**

Pada masa kini, teknologi pembungkusan litar bersepadu (IC) menjadi reka bentuk yang canggih di samping dapat mengekalkan kebolehpercayaan dan kualiti. Pakej skala cip flip (CSP) adalah salah satu daripada cip IC yang mempunyai wafertingkat yang dibungkus dengan bebola pateri sfera yang terletak di atas grid yang mana jaraknya telah ditentukan di antara cip. Untuk membungkusnya, acuan isian bawah (MUF) telah digunakan dan ia merupakan proses yang lebih mudah dan lebih cepat. Walau bagaimanapun, aliran sebatian acuan epoksi (EMC) yang tidak konsisten semasa pengkapsulan yang lebih mudah terdedah kepada corak pengisian yang tidak seimbang, pengisian tidak lengkap dan kekosongan dalaman. Kerana itu, proses pengisian dan aliran EMC melalui flip cip sangat sukar untuk digambarkan dengan eksperimen sebenar. Dalam kajian ini, pendekatan berangka telah digunakan untuk mengkaji proses pembungkusan flip cip dalam rerongga. Oleh itu, analisis berangka adalah pendekatan yang sesuai untuk digambarkan semasa proses pembungkusannya. Perisisan ANSYS FLUENT pula telah digunakan untuk mensimulasi dan menganalisis fenomena aliran cecair dan akibatnya. Teknik jumlah cecair (VOF) telah digunakan untuk menvisualisasi aliran MUF di rongga kosong dan cip flip yg berganda telah dibentangkan. Kajian terhadap tingkah laku aliran EMC dalam model rheologi yang berbeza juga telah dijalankan. Model Castro Macosko telah dikenal pasti sebagai model reologi yang terbaik untuk mempelajari perilaku aliran kerana ia telah mempertimbangkan kesan pengawetan dan tahap penukaran. Analisis berangka diteruskan pada kesan susunan flip cip. Susunan

berganda tiga cip flip mempunyai aliran pengurangan yang lebih tinggi dan peratusan jumlah udara terbentuk terbesar semasa pembungkusan. Hubungan kesan rheologi ke atas reka bentuk flip cip telah dikaji dengan sewajarnya. Perubahan kesan rheologi dan reka bentuk susun telah mempengaruhi sifat-sifat EMC seperti halaju, kadar ricih dan kelikatan.

#### NUMERICAL ANALYSIS DURING ECAPSULATION PROCESS OF MOLDED UNDERFILL WITH MULTI FLIP CHIP PACKAGE

#### ABSTRACT

Nowadays, the technology of Integrated Circuit (IC) packaging has become a sophisticated design in addition to maintaining reliability and quality. Flip Chip Scale Package (CSP) is one of the IC chips which has a wafer-level packaged with spherical solder bump located on a grid with a pre-defined pitch between chip. In order to package it, Molded Underfill (MUF) was used which was an easier and faster process. However, the inconsistent flow of Epoxy Molding Compound (EMC) during encapsulation was more susceptible to unbalanced filling pattern, incomplete filling and internal void. Therefore, the EMC filling and flow through flip chip is very hard to visualize with actual experiment. In this study, the numerical approaches were used to study the encapsulation process of multi flip chip in the cavity. Thus, the numerical analysis is an appropriate approach to visualize during the encapsulation process. ANSYS FLUENT was used to simulate and analyze the fluid flow phenomena and consequences. The volume of fluid (VOF) technique was used for visualization of flow front. The flow visualization of MUF in the empty cavity and multi flip chip were presented. The flow behavior of EMC in different rheology models have been conducted. The Castro Macosko model has been identified as the best model to study flow behavior since it has considered the curing effect and degree of conversion. The numerical analysis is continued on stacking effect of flip chip. Triple stacked multi flip chip was found to have high retardation flow and large volume percentage during encapsulation. The relationship of rheological effect on stacking design of flip chip were studied accordingly. Changes in rheological effect and stacking design have influenced the EMC properties such as velocity, shear rate and viscosity.

#### **CHAPTER ONE**

#### INTRODUCTION

#### 1.1 Overview of Integrated Circuit Packaging

Integrated Circuit (IC) packaging is a final manufacturing process of semiconductor device which encapsulated with semiconducting material in order to prevent from physical damage. Higher demand by electronic industries for IC package in order to get high performance required a great design to maintain its reliability and quality of electronic devices (Wan et al., 2007). Development of IC package is dynamic technology that always need an improvement in design and has multi function. There are many types of IC package have been produce to fill the industrial needs.

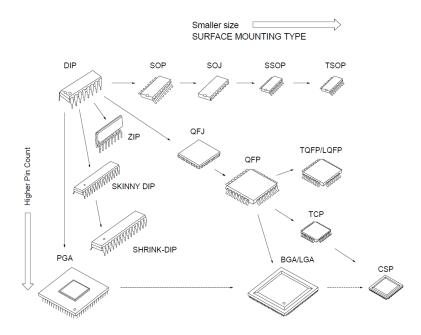

IC package can be categorised into three type of packages, which are through-hole mount package (THM), surface mount package (SMT) and chip scale package (CSP). Figure 1.1 shows the trend of IC package change from through-hole mount package to chip scale package (Anon, 2001). The design of IC package evolve from large design to smaller design and the evolution of their trend also grow same as the technology devices nowadays. Recently, CSP become one of the popular IC package because of its trend toward smaller, lighter and thinner where it meets application's demand (Khor & Abdullah, 2013). The combination of its performance and its small size make it become ideal solution for electronic manufacturing.

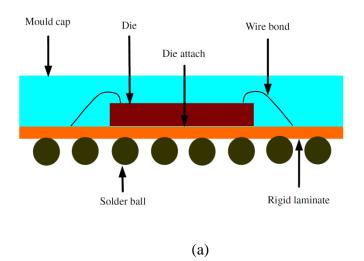

Figure 1.1: Trend of IC Package (Anon, 2001)

CSP is a single die which its package is 1.2 times the size of the die and it is is an evolution of surface mount package. There are many types of CSP and the most popular in CSP are flip chip ball grid arrays (FCBGA) and wire bond ball grid arrays (WBGA). Figure 1.2 (a) shows the cross section of WBGA and it consist of the interconnection between substrate and die using wire. The die attach directly to the substrate and the active surface of the die face upward, then its looped and bonded to the substrate. Since the current trend to get smaller and higher input/output, it can be one of the challenging to the electronic industry. It needs more wire to be bond in the package. Hence, the industry will face a production problem and increase the cost.

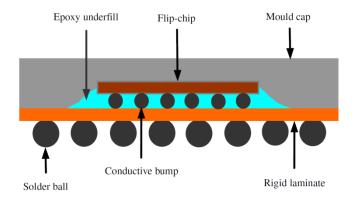

The flip chip technology is introduced to tackle this problem by the die is connected to subtrate with conductive bump (Wan et al., 2007). Figure 1.2 (b) shows the cross section of FCBGA package where the interconnection between chip and

subtrate by solder bump. The active surface of chip is flipped and attached to the solder bump, which is attached to the subtrate.

In flip chip technology, the gap between substrate and chip is underfilled with highly filled epoxy system. Underfill is one of important part in flip chip package where it provides a good reliability and quality. It can be classified into capillary underfill (CUF), no-flow underfill (NUF) and molded underfill (MUF) (Wong & Wong, 1999; Joshi et al., 2010).

(b)

Figure 1.2: (a) WBGA (b) FCBGA (Wan et al., 2007)

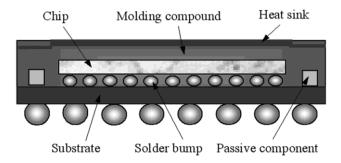

#### 1.2 Molded Underfill of Flip Chip Package

Molded underfill (MUF) is a process used in IC packaging to fill the gap between the chip and subtrate, and encapsulate the whole chip (over molding). Figure 1.3 shows the cross section of single MUF of flip chip package. Increased functionality requirement and advance in packaging technology made MUF is the right choice for alteration of flip chip design. The advantages of using MUF are lower material cost, save time production and provide excellent reliability for advanced electronic application (Chen et al., 2013). Besides that, MUF process is simple and faster compared to CUF (Joshi et al., 2010). Epoxy Mold Compound (EMC) is a solid epoxy based resin with fillers that has been used as a molded underfill material for encapsulation in order to protect the die and the solder bump from the stress and temperature effect (Khor et al., 2011). Figure 1.4 show EMC flow through the flip chip package during encapsulation process.

Figure 1.3: Cross section of Single Molded Underfill of Flip Chip Package (Chen, 2008)