# ANALYTICAL MODELLING OF BREAKDOWN EFFECT IN GRAPHENE NANORIBBON FIELD EFFECT TRANSISTOR

# MAHDIAR HOSSEINGHADIRY

UNIVERSITI SAINS MALAYSIA 2014

# ANALYTICAL MODELLING OF BREAKDOWN EFFECT IN GRAPHENE NANORIBBON FIELD EFFECT TRANSISTOR

by

# MAHDIAR HOSSEINGHADIRY

Thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

January 2014

# **ACKNOWLEDGEMENTS**

I would like to thank Dr. Asrulnizam for his enlightening guidance, kindness and support through this research. In addition I am very grateful of Dr. Ahmadi for his advices and helps. Many thanks to Mahdieh Nadi and our parents who have been always supporting. Furthermore, I am grateful for receiving financial aid from Universiti Sains Malaysia through PhD fellowship scheme. Finally I would like to thank all my friends, Mehdi khiabani, Mehdi Saiedmanesh, Arash Bahadorian, and Mahmood Pesaran for their help and support.

# TABLE OF CONTENTS

| Ackn              | owledgements                                       | ii    |

|-------------------|----------------------------------------------------|-------|

| Table of Contents |                                                    |       |

| List o            | of Tables                                          | vii   |

| List o            | of Figures                                         | viii  |

| List o            | of Symbols                                         | xiv   |

| List o            | of Abbreviation                                    | xviii |

| Abstr             | ak                                                 | XX    |

| Abstr             | act                                                | xxii  |

| CHA               | PTER 1 – INTRODUCTION                              |       |

| 1.1               | Overview                                           | 1     |

| 1.2               | Background                                         | 1     |

| 1.3               | Problem statement                                  | 5     |

| 1.4               | Research limitations and assumptions               | 5     |

| 1.5               | Research objectives.                               | 6     |

| 1.6               | Research Methodology                               | 6     |

|                   | 1.6.1 Length of saturation velocity region         | 7     |

|                   | 1.6.2 Impact ionization coefficient                | 7     |

|                   | 1.6.3 Breakdown mechanism                          | 7     |

| 1.7               | Thesis organisation                                | 8     |

| CHA               | PTER 2 – BASIC CONCEPT OF FIELD EFFECT TRANSISTORS |       |

| 2.1               | Overview                                           | 10    |

| 2.2               | Field effect transistors (FET) and its issues      | 10    |

| 2.3               | Length of velocity saturation region               | 11    |

| 2.4               | Impact ionization                                  | 12    |

| 2.5                     | Lateral  | breakdown                                                                     | 14 |

|-------------------------|----------|-------------------------------------------------------------------------------|----|

|                         | 2.5.1    | Multiplication coefficient and ionization integral                            | 15 |

|                         | 2.5.2    | Avalanche breakdown                                                           | 16 |

| 2.6                     | Down     | scaling problems                                                              | 17 |

| 2.7                     | Carbor   | n-based devices.                                                              | 21 |

|                         | 2.7.1    | Advantages of graphene-based electronics                                      | 22 |

|                         | 2.7.2    | Disadvantages of graphene-based electronics.                                  | 23 |

|                         | 2.7.3    | Application of graphene in electronics                                        | 25 |

|                         |          | 2.7.3(a) Applications of graphene in digital electronics                      | 25 |

|                         |          | 2.7.3(b) Application of graphene in analogue electronics                      | 26 |

|                         | 2.7.4    | Important graphene parameters in connection with FETs                         | 27 |

|                         |          | 2.7.4(a) Bandgap                                                              | 27 |

|                         |          | 2.7.4(b) Mobility                                                             | 31 |

|                         |          | 2.7.4(c) High-field transport                                                 | 33 |

|                         |          | 2.7.4(d) Two-dimensional nature of graphene                                   | 35 |

| 2.8                     | Length   | of velocity saturation region                                                 | 36 |

| 2.9                     | Ionizat  | ion coefficient                                                               | 41 |

| 2.10                    | Graphene |                                                                               | 45 |

|                         | 2.10.1   | Experimental works and analytical models related to carbon-based electronics. | 46 |

|                         | 2.10.2   | Review of the most important graphene-based transistors                       | 49 |

| CHAPTER 3 – METHODOLOGY |          |                                                                               |    |

| 3.1                     | Length   | of velocity saturation region $(L_d)$                                         | 54 |

|                         | 3.1.1    | 1D Model for Single-gate GNRFET                                               | 54 |

|                         | 3.1.2    | 1D Model for Double-gate GNRFET                                               | 59 |

|                         | 3.1.3    | 2D Model for Double-gate GNRFET                                               | 61 |

| 3.2                     | Ionizat  | ion coefficient                                                               | 66 |

|                                         | 3.2.1   | Verifying the models' assumptions                         | 66  |

|-----------------------------------------|---------|-----------------------------------------------------------|-----|

|                                         | 3.2.2   | The proposed model for ionization coefficient.            | 70  |

|                                         |         | 3.2.2(a) Ballistic motion                                 | 71  |

|                                         |         | 3.2.2(b) Drift motion                                     | 72  |

|                                         | 3.2.3   | Ionization threshold energy                               | 73  |

| 3.3                                     | Breakd  | lown voltage                                              | 74  |

|                                         | 3.3.1   | Single-gate GNRFET                                        | 74  |

|                                         | 3.3.2   | Double-gate GNRFET                                        | 75  |

| CTT                                     |         |                                                           |     |

| CHA                                     | PTER 4  | <ul> <li>RESULTS AND DISCUSSION</li> </ul>                |     |

| 4.1                                     | Lateral | electric field and length of velocity saturation region   | 76  |

|                                         | 4.1.1   | Single-gate GNRFET                                        | 76  |

|                                         | 4.1.2   | Double-gate GNRFET                                        | 79  |

|                                         |         | 4.1.2(a) 1D Model                                         | 79  |

|                                         |         | 4.1.2(b) 2D Model                                         | 81  |

|                                         | 4.1.3   | Comparison between single- and double-gate GNRFETs        | 84  |

| 4.2                                     | Ionizat | ion coefficient                                           | 86  |

| 4.3                                     | Breakd  | lown Voltage                                              | 90  |

|                                         | 4.3.1   | Single-gate GNRFET                                        | 90  |

|                                         | 4.3.2   | Double-gate GNRFET                                        | 93  |

|                                         | 4.3.3   | Comparison between breakdown voltage of DG- and SG-GNRFET | 97  |

|                                         | 4.3.4   | Comparison with silicon counter part devices.             | 98  |

| 4.4                                     | Validat | ion range of the proposed model                           | 99  |

| CHAPTER 5 – CONCLUSION AND FUTURE WORKS |         |                                                           |     |

|                                         |         |                                                           | 101 |

| 5.1                                     |         |                                                           | 101 |

| 5.2                                     | Future  | works                                                     | 103 |

| References                                                           | 104 |

|----------------------------------------------------------------------|-----|

| APPENDICES                                                           | 111 |

| APPENDIX A – DEFINITION OF IMPORTANT PARAMETERS IN MODELLING OF FETS | 112 |

| APPENDIX B – LIST OF PUBLICATIONS                                    | 117 |

| B.1 Published and accepted articles                                  | 117 |

# LIST OF TABLES

|           |                                                                                                                            | Page |

|-----------|----------------------------------------------------------------------------------------------------------------------------|------|

| Table 2.1 | Application of surface potential in modelling of different device characteristics                                          | 37   |

| Table 2.2 | Application of surface potential in modelling of different device characteristics                                          | 40   |

| Table 2.3 | Application of surface potential in modelling of different device structures                                               | 40   |

| Table 2.4 | The most important papers presenting ionization coefficient models in conventional semiconductors.                         | 42   |

| Table 2.5 | Important review papers and other works related to various topics on graphene                                              | 46   |

| Table 2.6 | Important models proposed for different properties of graphene                                                             | 47   |

| Table 4.1 | Default value for parameters used in simulation. Some values such as channel length and GNR's width may treat as variable. | 77   |

| Table 4.2 | Breakdown voltage of GNRFET compared to existed experimental data for silicon-FETs in different technologies.              | 98   |

# LIST OF FIGURES

|            |                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

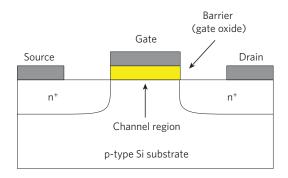

| Figure 1.1 | Conventional MOSFET with isolated gate from channel using oxide. Each FET consists of four main parts, drain, source, gate and channel. Gate is responsible to control conductivity of the channel and establish current flow between drain and source.                                                                                                                                                                     | 2    |

| Figure 1.2 | Graphene in form of a tube is called carbon nanotube (CNT). Narrow sheet of graphene which is unzipped CNT is known as graphene nanoribbon (GNR)                                                                                                                                                                                                                                                                            | 3    |

| Figure 1.3 | Typical GNRFET with top gate and Au drain and source contacts. Graphene nanoribbon is used in channel to decrease the transistor switching time.                                                                                                                                                                                                                                                                            | 3    |

| Figure 1.4 | Flow chart used to conduct this project.                                                                                                                                                                                                                                                                                                                                                                                    | 8    |

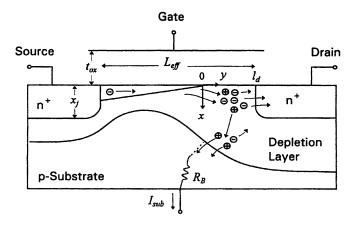

| Figure 2.1 | Conventional FETs. Schematic cross section of an n-type bulk silicon FET. (Extracted from (Schwierz, 2010))                                                                                                                                                                                                                                                                                                                 | 11   |

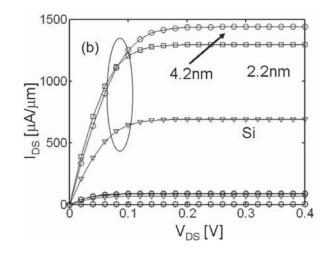

| Figure 2.2 | FET transfer characteristics showing $I_D$ against the gate-source voltage, $V_{gs}$ . Increasing $V_{ds}$ causes the current to increase. However, after a certain $V_{ds}$ , which is called saturation voltage $(V_{th})$ a saturation point is reached and the current does not increase as $V_{ds}$ increases.                                                                                                         | 11   |

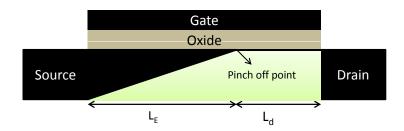

| Figure 2.3 | Length of velocity saturation region $L_d$ and pinch off point. At high electric field, carriers velocity reaches a saturation velocity and current saturates. Impact ionization occurs in the region between pinch-off and drain.                                                                                                                                                                                          | 12   |

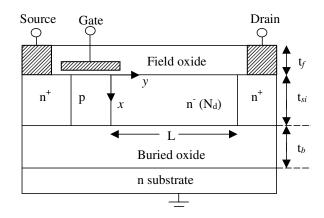

| Figure 2.4 | A typical power transistor with drift region outside gate area. The $t_f$ , $t_b$ , $t_{si}$ are front oxide, back oxide, channel thickness respectively and $L$ is the length of drift region or $L_d$ . In conventional power devices, increasing drift region length $(L)$ causes the breakdown voltage to increase. (Figure has been extracted from (Yang et al., 2005))                                                | 13   |

| Figure 2.5 | Avalanch breakdown and substrate current in a typical FET. Impact ionization results in substrate current, which is undesired characteristic in conventional FETs. (Extracted from (Wong, 2000)).                                                                                                                                                                                                                           | 17   |

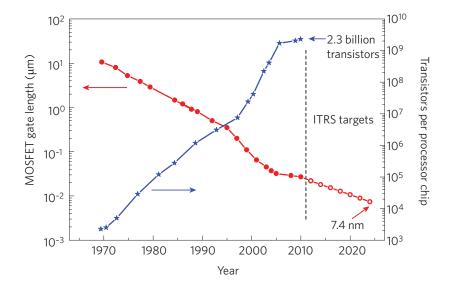

| Figure 2.6 | Trends in the number of transistors per digital chips and transistor channel. To keep up with this trends length of channel in transistors has been reduced. However, this shrinking cannot continue for too long, which is why new structures such double-gate FETs and new materials like graphene have been introduced hoping to reach even shorter length and higher processing speed. (Extracted from (Schwierz, 2010) | 18   |

|            | (Schwierz, 2010)                                                                                                                                                                                                                                                                                                                                                                                                            | 18   |

| Figure 2.7     | Mispositioned CNT resulting in current variation in CNTFETs. (Extracted from (Patil et al., 2008))                                                                                                                                                                                                                                                                                                                                                                                             | 25 |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.8     | A schematic of the fabricated CMOS inverter (a) and Fermi level repositioning in order to implement p-type and n-type FET (b). (Extracted from (Traversi et al., 2009))                                                                                                                                                                                                                                                                                                                        | 26 |

| Figure 2.8(a)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

| Figure 2.8(b)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

| Figure 2.9     | An AND logic gate (a and b) employing mono-layer graphene transistor. R is the output resistance of the graphene transistor, depending on the voltage of the gate $V_G$ . Obviously this kind of logic dissipates static power but benefits from very low delay using high mobility graphene mono-layer. Since making p-type and n-type channel is still a challenge the superiority of graphene has been verified using undoped channel and RTL logic. (Extracted from (Sordan et al., 2009)) | 26 |

| Figure 2.10    | Bandgap in graphene. SL: single-layer; BL: bilayer; LA: large-area; GNR: graphene nanoribbon. As can be seen existence of bandgap in GNR and BL graphene has been shown by experimental and theoretical studies. However, large area graphene does not open bandgap (Extracted from (Schwierz, 2010))                                                                                                                                                                                          | 28 |

| Figure 2.11    | Armchair (a) and zigzag (b) forms of GNR. The direction of current is assumed from left to right (Lateral direction).                                                                                                                                                                                                                                                                                                                                                                          | 28 |

| Figure 2.11(a) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

| Figure 2.11(b) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

| Figure 2.12    | Bandgap versus nanoribbon width. As width of nanoribbon decreases the bandgap increases. (Han et al., 2007))                                                                                                                                                                                                                                                                                                                                                                                   | 29 |

| Figure 2.13    | Bandgap related to graphene and GNRs. a) an armchair GNR (ac-GNR) with length $L_{ac}$ and width $W_{ac}$ . b) band-structure for large-area graphene (i), GNR (ii), bi-layer graphene (iii), and bi-layer graphene under the influence of an electric field. (Extracted from (Schwierz, 2010))                                                                                                                                                                                                | 31 |

| Figure 2.13(a) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

| Figure 2.13(b) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

| Figure 2.14    | Electron mobility in conventional material such as iii-v compounds InSb, InAs, In <sub>0.5</sub> 3Ga <sub>0.47</sub> As, InP, GaAs, In <sub>0.49</sub> Ga <sub>0.51</sub> P, and GaN. The values of mobility are related to undoped material except the Si. Moreover two region are demonstrated to show the range of mobility in CNT and GNR provided by experimental and theoretical studies. The figure shows that GNR can present lower mobility than that of silicon at bandgap wider than almost 0.5 eV. (Extracted form (Schwierz, 2010)) | 32 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.15    | As the nanoribbon width is reduced the bandgap gets wider but unfortunately the mobility of graphene decreases from $10^6$ cm/Vs for W = 10 nm to $10^3$ cm/Vs for W = 2 nm. (Extracted from (Bresciani et al., 2010))                                                                                                                                                                                                                                                                                                                           | 33 |

| Figure 2.16    | drift velocity of electrons respect to electric field for large-area graphene (Extracted from (Shishir and Ferry, 2009))                                                                                                                                                                                                                                                                                                                                                                                                                         | 34 |

| Figure 2.17    | The effects of drain-source $V_{ds}$ and channel length $L$ on the length of velocity saturation region (Impact ionization length). The $L_d$ increases with $V_{ds}$ and channel length. (Extracted from (Wong, 2000))                                                                                                                                                                                                                                                                                                                          | 42 |

| Figure 2.18    | Ionization coefficient versus electric field ( $\varepsilon$ ) and ionization threshold energy ( $E_i$ ) employing different approaches. (Extracted from (Rubel et al., 2011))                                                                                                                                                                                                                                                                                                                                                                   | 45 |

| Figure 2.19    | a) Several structures to make transistors based on graphene. From left, back-gated, double-gated employing exfoliated graphene channel or graphene, which has been grown on metal, and top-gated with a channel of epitaxial graphene (Schwierz, 2010).                                                                                                                                                                                                                                                                                          | 50 |

| Figure 2.19(a) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |

| Figure 2.19(b) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |

| Figure 2.20    | Drain current against drain-source voltage in large-area graphene-based FET. a) Transfer characteristics consists of two linear regions and one saturation region. b) Transfer characteristics cross at high values of $V_{ds}$ meaning that the gate cannot control the current. (Extracted from (Curtis et al., 2009))                                                                                                                                                                                                                         | 52 |

| Figure 2.20(a) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

| Figure 2.20(b) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

| Figure 3.1     | Schematic cross section of a top-gated GNRFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55 |

| Figure 3.2     | Schematic cross section of a double-gate GNRFET (DG-GNRFET). The parameters $\xi_{sat}$ and $\xi_0$ are used interchangeably in this text.                                                                                                                                                                                                                                                                                                                                                                                                       | 59 |

| Figure 3.3     | Schematic cross section of a double-gate GNRFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| Figure 3.4    | Momentum relaxation mean free time and path $(\tau_n \text{ and } \lambda_m)$ as a function of energy. The values obtained from modelling (Eq. 3.55) and simulation (Tse et al., 2008) and have been compared together in this figure showing that equation $\lambda_m = v_F \tau_m$ is valid for calculation of $\lambda_m$ . | 67         |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3.4(a) |                                                                                                                                                                                                                                                                                                                                | 67         |

| Figure 3.4(b) |                                                                                                                                                                                                                                                                                                                                | 67         |

| Figure 3.5    | Average energy of electron versus electric field (a) at moderate strength (b) at high strength. Comparison of the modelled results using Eq. 3.59 with simulated data show that the proposed model agrees well with simulation.                                                                                                | 69         |

| Figure 3.5(a) |                                                                                                                                                                                                                                                                                                                                | 69         |

| Figure 3.5(b) |                                                                                                                                                                                                                                                                                                                                | 69         |

| Figure 3.6    | Profile of drift velocity against energy calculated from Eq. 3.60. Drift velocity saturates at $3.5 \times 10^5 m/s$ from 0.4 eV energy onward.                                                                                                                                                                                | 70         |

| Figure 3.7    | typical carrier trajectory and the associated energy gain. As carrier experience the lateral electric field, it gains energy from field. During the path along the direction of electric field it may lose its energy due to collisions. (Figure extracted from (Rubel et al., 2011))                                          | 71         |

| Figure 3.8    | Number of carbon atoms in traverse direction and the vertical distance between two carbon atoms                                                                                                                                                                                                                                | 73         |

| Figure 4.1    | Lateral electric field of SG-GNRFET at different drain voltages. The highest electric field is seen at drain junction.                                                                                                                                                                                                         | 78         |

| Figure 4.2    | The $L_d$ of SG-GNRFET at different $L$ and $V_{ds}$ .                                                                                                                                                                                                                                                                         | <b>7</b> 9 |

| Figure 4.3    | The $L_d$ of SG-GNRFET vs. $t_{ox}$ variations at different drain voltages.                                                                                                                                                                                                                                                    | <b>7</b> 9 |

| Figure 4.4    | Lateral electric field of DG-GNRFET at different positions from drain junction.                                                                                                                                                                                                                                                | 80         |

| Figure 4.5    | The $L_d$ of DG-GNRFET at different channel lengths and drain voltages.                                                                                                                                                                                                                                                        | 80         |

| Figure 4.6    | The $L_d$ of DG-GNRFET vs. oxide thickness variations at different drain voltages.                                                                                                                                                                                                                                             | 81         |

| Figure 4.7    | Comparison of the results extracted from 2D numerical simulator and model.                                                                                                                                                                                                                                                     | 82         |

| Figure 4.8    | The effect of drain-source voltage on the profile of surface potential, and lateral electric field distribution using the proposed model. Default parameters are $N_d = 5 \times 10^{25}$ m <sup>-3</sup> , $L = 20nm$ , $t_{ox} = 1$ nm, and graphene film thickness $t_G = 0.4$ nm.                                          | 83         |

| Figure 4.8(a)  |                                                                                                                                                                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.8(b)  |                                                                                                                                                                                                                                                   |

| Figure 4.9     | The effect of doping concentration (a) and oxide thickness (b) on the lateral electric field and length of saturation velocity region. Default parameters are $N_d = 5 \times 10^{25} m^{-3}$ , $L = 20$ nm, $t_{ox} = 1$ nm, and $t_G = 0.4$ nm. |

| Figure 4.9(a)  |                                                                                                                                                                                                                                                   |

| Figure 4.9(b)  |                                                                                                                                                                                                                                                   |

| Figure 4.10    | The effect of channel length and doping concentration on the length of saturation velocity region. Default parameters are $N_d = 5 \times 10^{25} m^{-3}$ , $L = 20$ nm, $t_{ox} = 1$ nm, and $t_G = 0.4$ nm.                                     |

| Figure 4.10(a) |                                                                                                                                                                                                                                                   |

| Figure 4.10(b) |                                                                                                                                                                                                                                                   |

| Figure 4.11    | Profile lateral electric field against distance from drain for DG- and SG-GNRFET. Horizontal axis is the distance from drain in nm.                                                                                                               |

| Figure 4.12    | The profile of velocity saturation region length respect to, drain-source voltage (a), oxide thickness (b), and channel length (c). As can be seen, double-gate FET suppress the length of drain region.                                          |

| Figure 4.12(a) |                                                                                                                                                                                                                                                   |

| Figure 4.12(b) |                                                                                                                                                                                                                                                   |

| Figure 4.12(c) |                                                                                                                                                                                                                                                   |

| Figure 4.13    | Ionization coefficient of GNR versus reciprocal electric field (a) at high strength compared to ionisation coefficient of silicon extracted from (Yeom et al., 1996) (b) at very high strength.                                                   |

| Figure 4.13(a) |                                                                                                                                                                                                                                                   |

| Figure 4.13(b) |                                                                                                                                                                                                                                                   |

| Figure 4.14    | Ionization coefficient of GNR versus electric field compared to that of silicon. Solid lines shows the results of Monte Carlo simulation from (Ghadiry et al., 2013).                                                                             |

| Figure 4.15    | Results of simulation of threshold energy using Guassian atomic simulator (Frisch et al., 2009) and the ratio of $E_t$ over $E_g$ .                                                                                                               |

| Figure 4.16    | Breakdown voltage SG-GNRFET at different oxide thickness and channel length. (a) $L=15~\rm nm$ (b) $L=30~\rm nm$                                                                                                                                  |

| Figure 4.16(a) |                                                                                                                                                                                                                                                   |

| Figure 4.16(b) |                                                                                                                                                                                                                                                  | 91  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.17    | Breakdown voltage for single-gate GNRFET at different GNR's width and channel length                                                                                                                                                             | 92  |

| Figure 4.17(a) |                                                                                                                                                                                                                                                  | 92  |

| Figure 4.17(b) |                                                                                                                                                                                                                                                  | 92  |

| Figure 4.18    | The gate-source voltage versus lateral electric field at the drain region. Different channel length is applied as well as gate-source voltage.                                                                                                   | 93  |

| Figure 4.19    | Breakdown voltage of single-gate GNRFET against gate voltage at different channel length.                                                                                                                                                        | 94  |

| Figure 4.20    | Breakdown voltage for double-gate graphene nanoribbon transistor at different oxide thickness and channel length                                                                                                                                 | 95  |

| Figure 4.20(a) |                                                                                                                                                                                                                                                  | 95  |

| Figure 4.20(b) |                                                                                                                                                                                                                                                  | 95  |

| Figure 4.21    | Breakdown voltage for DG-GNRFET at different GNR's width and channel length                                                                                                                                                                      | 96  |

| Figure 4.21(a) |                                                                                                                                                                                                                                                  | 96  |

| Figure 4.21(b) |                                                                                                                                                                                                                                                  | 96  |

| Figure 4.22    | Breakdown voltage of single-gate GNRFET against gate voltage                                                                                                                                                                                     | 97  |

| Figure 4.23    | A comparison between breakdown voltage of single and double-gate GNRFET at different GNR's width, channel length, and oxide thickness. It shows that breakdown voltage of a double-gate device is almost half the BV of single-gate counterpart. | 100 |

| Figure 4.23(a) |                                                                                                                                                                                                                                                  | 100 |

| Figure 4.23(b) |                                                                                                                                                                                                                                                  | 100 |

| Figure 4 23(c) |                                                                                                                                                                                                                                                  | 100 |

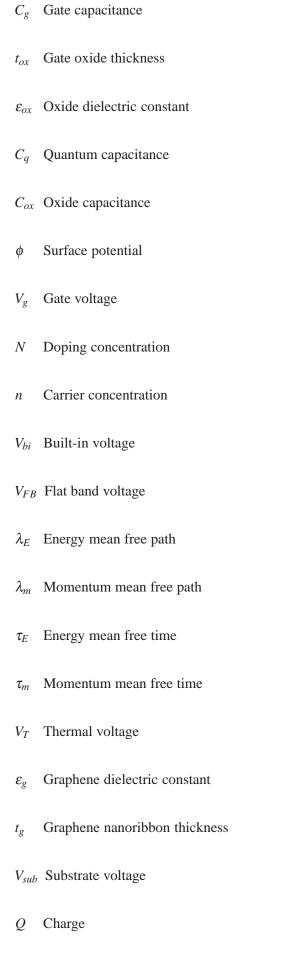

# LIST OF SYMBOLS

| angle in radians                     |

|--------------------------------------|

| Length of velocity saturation region |

| Ionization coefficient               |

| Gate-source voltage                  |

| Transistor threshold voltage         |

| Drain saturation voltage             |

| Drain-source voltage                 |

| Drain current                        |

| Channel length                       |

| Effective channel length             |

| Breakdown voltage                    |

| Front gate oxide thickness           |

| Back gate oxide thickness            |

| Silicon channel thickness            |

| Electric field strength              |

| Charge magnitude                     |

| Ionization threshold energy          |

|                                      |

Lateral distance

| M(x) Multiplication factor                     |

|------------------------------------------------|

| $\alpha_n$ Ionization coefficient of electrons |

| $\alpha_p$ Ionization coefficient of holes     |

| I <sub>sub</sub> Substrate current             |

| a Graphene lattice constant                    |

| $m_h$ Hole effective mass                      |

| $m_e$ Electron effective mass                  |

| $m_0$ Free electron mass                       |

| Ion On current of FET                          |

| $I_{off}$ Off current of FET                   |

| $V_{tn}$ N-channel threshold voltage           |

| $V_{tp}$ P-channel threshold voltage           |

| f Frequency                                    |

| $E_g$ Bandgap energy                           |

| ħ Reduced Plank's Constant                     |

| $W_g$ GNR's width                              |

| $v_F$ Fermi Velocity                           |

| $\mu_{FE}$ Field effect mobility               |

| $g_m$ Transconductance                         |

| V <sub>s</sub> Drain-Source voltage            |

$\phi_{ch}$  Surface potential at the centre of the channel  $n_{2D}$  2D carrier concentration  $f(E-E_F)$  Fermi Dirac distribution function **Boltzmann Constant** TTemperature  $E_{Fs}$  Source Fermi Energy  $E_{Fd}$  Drain Fermi Energy Lateral electric field mass density of graphene  $v_p h$  Sound velocity in 2D graphene Acoustic deformation potential DGroup velocity in graphene  $v_g$  $v_{sat}$  Saturation velocity of carriers  $\omega_{op}$  Optical phonon frequency

Nop Occupation number

# LIST OF ABBREVIATION

| LVSR Length of Velcity Saturation Region                |

|---------------------------------------------------------|

| FET Field Effect Transistor                             |

| GNR Graphene Nanoribbon                                 |

| CNT Carbon Nanotube                                     |

| Sat Saturation                                          |

| MOSFET Metal Oxide Field Effect Transistor              |

| BJT Bipolar Junction Transistor                         |

| CMOS Complementary Metal Oxide Field Effect Transistor  |

| PDP Power Delay Product                                 |

| ITRS International Roadmap for Semiconductor Technology |

| GNRFET Graphene Nanoribbon Field Effect Transistor      |

| SG Single Gate                                          |

| <b>DG</b> Double Gate                                   |

| APD Avalanche Photo Diode                               |

| <b>HEMT</b> High Electron Mobility Transistor           |

| <b>2D</b> Two-Dimensional                               |

| 1D One-Dimensional                                      |

| RTL Resistor Transistor Logic                           |

- **BL** Bilayer

- SL single Layer

- **3D** Three-Dimensional

- ES Equilibrium State

- LB Lucky Ballistic

- LD Lucky Drift

**CNTFET** Carbon Nanotube Field Effect Transistor

# PEMODELAN ANALITIKAL KESAN PECAH RUNTUH TRANSISTOR KESAN MEDAN NANORIBBON GRAPHENE

#### ABSTRAK

Sejak tahun 2004, aplikasi graphene sebagai saluran transistor telah menjadi tumpuan kerana kelebihan dari segi berskala luar biasa dan mempunyai mobiliti pembawa yang tinggi. Permodelan kesan voltan runtuh (BV) terhadap transistor medan elektrik graphene nanoribbon ( GNRFET ) diperlukan untuk mengkaji had voltan operasi untuk transistor. Walau bagaimanapun, sehingga kini tiada kajian yan terperinci mengenai pendekatan analisis dan pemodelan pada kesan BV untuk transistor yang berasaskan graphene. Oleh itu, tujuan projek ini adalah untuk mewujudkan model separuh analisis untuk medan elektrik sisi, panjang halaju kawasan ketepuan (LVSR), pekali pengionan ( $\alpha$ ), dan voltan runtuh transistor medan nanoribbon graphene (GNRFET). Metodologi projek ini di mana mengaplikasikan undang-undang Gauss di kawasan saliran dan punca untuk menerbitkan persamaan potensi permukaan dan medan elektrik sisi. Setelah itu,LVSR dihitungkan sebagai penyelesaian untuk potensi permukaan pada keadaan tepu. Pengionan pekali dimodelkan dan dihitungkan dengan menerbitkan persamaan kebarangkalian perlanggaran dalam mod balistik dan hanyut dengan berdasarkan teori hanyutan bertuah pengionan. Tenaga ambang pengionan dihitungkan dengan menggunakan simulasi dan persamaan empirikal yang diterbitkan daripada analitikal separuh. Akhirnya keadaan pecahan runtuhan digunakan untuk menghitungkan BV sisi. Hasil daripadakajian ini, model analisis dan separa analisis yang mudah telah dicadangkan untuk LVSR,  $\alpha$ , dan BV, yang boleh digunakan di dalam mereka bentuk dan pengoptimuman peranti semikonduktor dan penderia yang berasaskan graphene. Aplikasi penggunaan persamaan yang dicadangkan BV telah dikaji dengan keadaan situasi yang berbeza iaitu panjang saluran, bekalan voltan,ketebalan oksida, lebar GNR dan voltan get. Keputusan simulasi menunjukkan voltan operasi FET boleh serendah 0.25 V untuk mengelakkan pecah runtuh. Walaubagaimanapun, selepas pengoptimuman ia boleh dicapai sehingga 1.5 V.

# ANALYTICAL MODELLING OF BREAKDOWN EFFECT IN GRAPHENE NANORIBBON FIELD EFFECT TRANSISTOR

#### **ABSTRACT**

Since 2004, graphene as transistor channel has drawn huge amount of attention due to its extraordinary scalability and high carrier mobility. In order to open required bandgap, its nanoribbon form is used in transistors. Breakdown effect modelling of the graphene nanoribbon field effect transistors (GNRFET) is needed to investigate the limits on operating voltage of the transistor. However, until now there is no study in analytical approach and modelling of the breakdown voltage (BV) effects on the graphene-based transistors. Thus, in this project, semi-analytical models for lateral electric field, length of velocity saturation region (LVSR), ionization coefficient (\alpha), and breakdown voltage (BV) of single- and double-gate graphene nanoribbon field effect transistors (GNRFET) are proposed. As the methodology, the application of Gauss's law at drain and source regions is employed in order to derive surface potential and lateral electric field equations. Then, LVSR is calculated as a solution of surface potential at saturation condition. The ionization coefficient is modelled and calculated by deriving equations for probability of collisions in ballistic and drift modes based on lucky drift theory of ionization. Then the threshold energy of ionization is computed using simulation and an empirical equation is derived semi-analytically. Finally avalanche breakdown condition is employed to calculate the lateral BV. As a result of this research, simple analytical and semi-analytical models are proposed for the LVSR,  $\alpha$ , and BV, which could be used in design and optimization of semiconductor devices and sensors. The proposed equations is used to examine the BV at

different situations of various channel lengths, supply voltages, oxide thickness, GNR widths, and gate voltages. Simulation results show the operating voltage of FETs could be as low as 0.25 V in order to prevent breakdown. However, after optimizations it can be reached to 1.5 V.

#### **CHAPTER 1**

## INTRODUCTION

#### 1.1 Overview

In this section, firstly, a brief background is presented to explain the issues connected with CMOS scaling and breakdown voltage. Secondly, the research objectives, scope, plan, and a brief methodology of this project are expressed.

## 1.2 Background

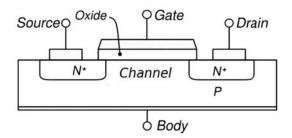

Metal oxide field effect transistor (MOSFET) as shown in Fig. 1.1 has been the most used semi-conducting device for low power logic circuits, power MOSFETs and analogue applications. The key advantages of MOSFET compared to previous counterparts such as resistor-transistor logic (RTL) and bipolar-junction transistor (BJT) are its low power consumption and high input impedance due to isolation of gate from channel. However, high delay of CMOS (Complementary MOS) used in digital applications has been always an issue compared to high switching frequency of for example BJT logics.

For decades there has been a lot of improvements in lowering power and delay in MOS-FETs by changing the gate dielectric, altering the structure and using different layers, adding several gates leading to double-gate, triple gate and even surrounding gate MOSFETs to control the channel better, and obviously employing different channel material such as GaAs instead of silicon to increase the carrier velocity.

Figure 1.1: Conventional MOSFET with isolated gate from channel using oxide. Each FET consists of four main parts, drain, source, gate and channel. Gate is responsible to control conductivity of the channel and establish current flow between drain and source.

Alternatively, shrinking transistor sizes has been one of the most significant solutions for improving power-delay product (PDP). Reducing the channel length, results in lowering the channel resistance and delay. In addition, it causes the gate capacitance, which is the most important factor in logic gates' delay, to reduce (International roadmap for semiconductor thechnology (ITRS), 2013). Having said that, there are limitations, such as short channel effects, preventing scaling down to nanoscale dimensions and reaching desired characteristics.

When the channel length is comparable to the depletion region of the source and drain the device is called a short channel device. In short channel devices, short channel effect arises that limits the device performance.

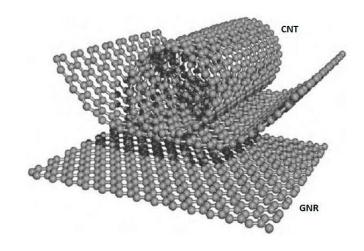

Therefore researchers have been trying to introduce new materials with higher mobility and scalability. In 2004, Geim and Nikolove (Novoselov et al., 2004) managed to produce stable graphene- one atom thick layer of graphite at room temperature-and measure its mobility. As it was expected from previous theoretical studies, high carrier mobility was measured in graphene, which is a promise for future nanoelectronic devices. In addition to very high carrier velocity, it shows very high conductance, and tunable bandgap. However the main issue with graphene is its zero bandgap which makes it a very poor semiconducting material for application of FETs. Further studies on opening bandgap in graphene, resulted in introduction of Carbon Nanotube (CNT) and graphene nanoribbon (GNR). Fig. 1.2 shows typical samples of

Figure 1.2: Graphene in form of a tube is called carbon nanotube (CNT). Narrow sheet of graphene which is unzipped CNT is known as graphene nanoribbon (GNR)

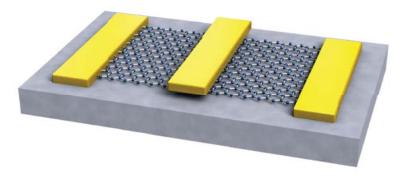

Figure 1.3: Typical GNRFET with top gate and Au drain and source contacts. Graphene nanoribbon is used in channel to decrease the transistor switching time.

#### GNR and CNT.

Graphene nanoribbons are strips of graphene with narrow width normally less than 50 nm indicating notable electrical properties such as high mobility, high conductance and small bandgap (Novoselov et al., 2004). Recently, GNR has been introduced as an alternative material for the next generation of MOSFETs (Schwierz, 2010). Fig. 1.3 shows a typical graphene nanoribbon FET (GNRFET) with a top gate. Using graphene with thickness as low as possible, the adverse short channel effects in silicon-based MOSFETs could be solved. Therefore, the dimensions of the transistors could be scaled down extremely, which results in low propagation delay down to 0.025 ps (Sako et al., 2011).

However the benefits of GNR come with cost. Firstly, the bandgap opened in GNR is still not enough to secure a satisfactory  $I_{on}/I_{off}$  and in narrow ribbons, edge effects suppress the mobility to some values even less than that of silicon counterpart. Secondly, Fabrication of GNR is still a difficult and not accurate task (Schwierz, 2010). Despite great improvement in fabrication process of GNR, it is still not mature enough to be used in mass production and industry. However the research is still vastly going on in this field hoping to find solutions for these issues.

Due to difficulties in fabrication of GNR, many researchers take advantage of analytical modelling and computer simulation to extract details about properties of GNR and possibility of making applicable FETs using GNR. As a result, there are several models for properties of GNR and CNT in the literature. However, since graphene as channel material was introduced recently, there are still many unanswered questions to be explored on these materials. As an example, there has been no attempt to study the breakdown mechanism and ionization process of GNR analytically or experimentally.

Lateral breakdown, which will be the focus of this thesis, is a mechanism limiting the maximum voltage that can be tolerated before the beginning of large current flow between the drain and source in a FET. Prior to calculate the lateral breakdown voltage, impact ionization rate must be computed. Eqn. 1.1 shows the relation of impact ionization and breakdown voltage (Yang et al., 2005).

$$1 = \int_0^{L_d} \alpha dx \tag{1.1}$$

,where  $L_d$  is the length of saturation velocity region- a portion of channel between pinch-off point and drain- and  $\alpha$  is the impact ionization which is the number of electron-hole pairs created by a mobile carrier travelling a unit of distance along the lateral electric field Rubel et al., 2011).

When a sufficient electric field is applied between drain and source, mobile carriers gain enough energy to create electron hole pairs by colliding to lattice atoms resulting in impact ionization (Wong, 2000; Kim et al., 1996). This process (impact ionisation) defines the current which flows in the depletion region when a large electric field is applied.

In this thesis, a study on effects of lateral breakdown voltage of GNR-based FETs is conducted. As a results of this thesis, several analytical models are proposed for breakdown mechanism and safe operating voltage of typical devices is calculated analytically. In addition, future studies on design and optimization of related devices such as power FETs or avalanche photo diodes (APDs) could use the proposed approach here.

#### 1.3 Problem statement

Increasing the drain-source voltage ( $V_{ds}$ ) in FETs causes the drain-source current ( $I_{ds}$ ) to increase. However, there is a limit (breakdown voltage (BV)) in increasing  $V_{ds}$ . After that limit, the device does not function properly and either it conducts high amount of current or cut the current both being a failure in a circuit. Therefore, it is necessary to identify BV of any new material in the devices in order to limit the operating voltage. While in carbon-based FETs, which is the most important device in carbon-based digital and analogue circuits, there is shortage of research on breakdown voltage. Therefore, it was a motivation for us to examine the breakdown and ionization mechanisms in GNRFETs. In this project, an analytical approach is presented to calculate maximum operating voltage of GNRFETs.

## 1.4 Research limitations and assumptions

As fabrication of carbon-based devices requires sophisticated equipments such as advanced and accurate CVD (Chemical vapour deposition) machine, and precise photo lithography, fabrica-

tion is not possible with the available equipments in our university. Therefore, our research is limited to analytical models and computer simulations only. We only address lateral breakdown and ionization. In addition, among variety of devices such as bilayer-GNRFET, CNT-FET, we limit this project to mono-layer GNRFET for simplicity to make sure that we can achieve our objectives. However, both single-gate and double-gate FETs are modelled and breakdown voltage is calculated.

## 1.5 Research objectives

#### i. Objective 1

To propose analytical models for lateral electric field and length of velocity saturation region of GNR-based FETs

#### ii. Objective 2

To propose an analytical model for ionization coefficient and breakdown voltage of GNR-based FETs

#### iii. Objective 3

To simulate GNR-based FETs in terms of breakdown voltage and calculate the maximum operating voltage of the typical GNRFETs at different conditions

## 1.6 Research Methodology

The modelling in this project is divided into three different sections. The first section deals with surface potential, lateral electric field, and length of velocity saturation region. The secondly, section provides models for ionization coefficient, and in the last section the model for breakdown voltage is provided.

#### 1.6.1 Length of saturation velocity region

Surface potential will be modelled using application of Gauss law at drain and source regions of graphene nanoribbon channel. As Fig. 1.4 shows, the models are derived using one-dimensional approach for simplicity. Firstly, we start by applying Gauss's Law inside the channel to obtain Poison's Equation. Then surface potential is resulted by solving the Poison's Equation. By taking derivation, lateral electric field can be obtained. In addition, using the surface potential expression, the length of velocity saturation region is achieved.

#### 1.6.2 Impact ionization coefficient

Impact ionization model can be derived based on general lucky drift theory reported in Fawcett et al., 1970) and successfully used for semiconductors with parabolic bandstructure such as Si, GaAs etc (Rubel et al., 2011). In this method, it is assumed that a carrier can reach threshold energy in two ways. First it reaches threshold energy through a ballistic motion. Secondly, the carrier first undergos some collisions, then reaches the threshold energy. Therefore, the motion of electron is modelled in both drift and ballistic modes. First, an expression for characteristic length being the distance carriers travel before reaching threshold energy having no collision is derived. Then the probability of having no collision travelling characteristic length in both ballistic and drift modes is formulated. Adding two probabilities gives the total probability of reaching threshold energy. It is worth to mention that due to unusual properties of GNRs, significant modification must be made to the previous models, which are discussed in the relevant section.

#### 1.6.3 Breakdown mechanism

Finally, the breakdown voltage is modelled. The model relies on Fullop's integral, which has been used many times for calculation of BV in silicon-based transistors (Yang et al., 2005). In

## Literature Review ( GNRFETs, Surface potential and ionization coefficient models ) Developing m-file source code for Deriving surface potential model (Application of Guass law in channel) surface potential simulation Deriving lateral electric field and saturation Developing m-file source code for region model saturation region simulation (Solving surface potential model at saturation condition) Developing m-file source code for Deriving ionization coefficient model (Using lucky drift theory of ionization ) ionization coefficient simulation Developing m-file source code for Calculating BV (Fullup's integral) breakdown voltage simulation Finalizing the results and analysis thesis document submission

Thesis document submission

Figure 1.4: Flow chart used to conduct this project.

this method, firstly multiplication factor is calculated and then by equating the multiplication factor to infinity (avalanche breakdown condition), BV is calculated. The drain source voltage is increased until the avalanche condition is satisfied. The obtained  $V_{ds}$  is called breakdown voltage resulting in infinite multiplication factor. In summary, a flow chart shown in Fig. 1.4 is used to conduct this project.

### 1.7 Thesis organisation

This thesis is organized as follows. Chapter 2 provides the basic concepts regarding the length of saturation velocity region, ionization mechanism and lateral breakdown voltage. Furthermore useful equations and definitions will be provided there. In addition, more information will

be given focusing on the advantages and disadvantages of graphene, application of graphene in FETs and required equations and properties used in this thesis. Chapter 3 will review literature in three sections, surface potential models, ionization coefficient models and graphene-based transistors. In continue the methodology to conduct this research is presented in three sections of chapter 4 consisting three types of analytical models. The next chapter presents the simulation results based on the proposed models at different values of structural parameters. A comparison between double-gate (DG) and single-gate (SG) will be conducted as well. Chapter 5 presents a summary of this thesis, outlines the achieved results and recommends possible future works.

#### **CHAPTER 2**

# BASIC CONCEPT OF FIELD EFFECT TRANSISTORS

#### 2.1 Overview

In this chapter first the basic concept of FETs is introduced. In addition, in three subsections, the concepts related to the length of saturation velocity region, impact ionization and lateral breakdown are discussed. Finally, graphene is introduced as a candidate for transistor channel and its properties related to FET are studied.

#### 2.2 Field effect transistors (FET) and its issues

A FET, shown in (Fig. 2.1), is simply a device consisting of a gate, a channel region which connects the source and drain junctions, and a barrier which separates the channel from the gate. By controlling the channel conductivity in FETs the drain current increases or decreases. The channel conductivity varies by changing the applied voltage between gate and source. A threshold voltage  $V_t$  is defined in FETs as the minimum voltage of gate-source to form a conducting channel between drain and source.

There are three main regions in each voltage transfer characteristic, cut-off, linear and saturation. In cut-off state, where  $V_{gs} < V_{th}$  no conducting channel is formed and therefore no current flows. In the linear region,  $V_{gs} > V_{th}$  and  $V_{ds} < V_{sat}$ , where  $V_{sat}$  is the drain saturation voltage. In this region as  $V_{gs}$  increases, the current increases too almost linearly respect to  $V_{gs}$ . The last is saturation region (see Fig. 2.2), where as  $V_{ds}$  increases current increases slightly.

Figure 2.1: Conventional FETs. Schematic cross section of an n-type bulk silicon FET. (Extracted from (Schwierz, 2010))

Figure 2.2: FET transfer characteristics showing  $I_D$  against the gate-source voltage,  $V_{gs}$ . Increasing  $V_{ds}$  causes the current to increase. However, after a certain  $V_{ds}$ , which is called saturation voltage  $(V_{th})$  a saturation point is reached and the current does not increase as  $V_{ds}$  increases.

In this region carriers' speed reaches velocity saturation  $v_{at}$  and does not exceed that due to collisions, which deviate carriers from lateral direction and reduces their velocity.

## 2.3 Length of velocity saturation region

The effective channel length is one of the most important parameters of MOSFETs showing the portion of the channel that contribute to the properties of the MOS such as current-voltage (I-V) characteristic. In order to calculate effective channel length, which is  $I_E = L - L_d$ , the length of the drain region  $L_d$  has to be computed. The  $L_d$  controls the lateral drain breakdown voltage (Wong, 2000), substrate current, hot-electron generation (Arora and Sharma, 1991), and drain current at the drain region (Gildenblat et al., 2006). In a FET, if the applied drain

voltage is higher than the drain saturation voltage, the electric field near the drain junction will be higher than the critical field strength, which results in carrier velocity saturation. In addition, high electric field near the drain junction causes impact ionization (Wong and Poon, 1997). Saturation region is defined as the region between pinch-off point and drain (see Fig. 2.3).

Figure 2.3: Length of velocity saturation region  $L_d$  and pinch off point. At high electric field, carriers velocity reaches a saturation velocity and current saturates. Impact ionization occurs in the region between pinch-off and drain.

As reported in (Wong, 2000; Singh, 2005) the length of this region is used along with Fulop's Integral to calculate breakdown voltage (BV) in FETs. In high power devices, a drift region is normally formed outside the gate area to increase the breakdown voltage and length of saturation region is approximated to the length of drift region (Kim et al., 2010; Dang, 1977). Fig. 2.4 shows a schematic view of a typical power device. In this figure, the length of velocity saturation region  $L_d$  and the effective channel  $L_E$  separated by pinch-off point are shown.

## 2.4 Impact ionization

As the feature size of integrated MOS devices decreases further, the high electric field near the drain region becomes more crucial and poses a limit on the device operations, notably by a large gate current, substrate current and substantial threshold voltage shift, hot electron generation and drain breakdown caused by the impact ionization in the high field region near the drain. The key parameters for describing these mechanisms are the impact ionization rate

Figure 2.4: A typical power transistor with drift region outside gate area. The  $t_f$ ,  $t_b$ ,  $t_{si}$  are front oxide, back oxide, channel thickness respectively and L is the length of drift region or  $L_d$ . In conventional power devices, increasing drift region length (L) causes the breakdown voltage to increase. (Figure has been extracted from (Yang et al., 2005))

and the length of velocity saturation region.

The definition of impact ionization is the number of electron-hole pairs created by a mobile carrier travelling unit of distance through the depletion region along the direction of the electric field (Rubel et al., 2011). According to several previous works such as (Rubel et al., 2011), the electrons and holes impact ionization coefficients are strongly dependant on the electric field strength. It can be formulated as the inverse of the average distance travelled by a carrier prior to the ionization event and it is given by  $\alpha = P(F, E_t)/l_0$ , where  $P(F, E_t)$  is the probability that electron reaches threshold energy  $E_t$  defined as minimum energy required to free an electron (Ridley, 1983). In this equation,  $\alpha$  is the impact ionization coefficient of GNR, F is the electric field strength, and  $l_0 = E_t/qF$  is the distance travelled by carrier prior to impact ionization assuming no collision is possible.

Impact ionization is an important charge generation mechanism. It occurs in many semi-conductor/devices and it may either considered as beneficial characteristic of the device or it can result in unwanted parasitic effects (Maes et al., 1990). For example, it is exploited in avalanche photo diodes (APD).

An avalanche photodiode (APD) is light-sensitive electron device employing the photoelectric effect to interpret the intensity of the light to electricity. Applying high reverse bias (typically 100-200 V in silicon) results in a gain (roughly 100) caused by impact ionization and avalanche phenomenon.

#### 2.5 Lateral breakdown