# [ME08] Development of silicon planar P-I-N photodiode

#### P Susthitha Menon a/p N V Visvanathan, Sahbudin Shaari

Photonics Technology Laboratory (PTL), Institute of Micro Engineering and Nanoelectronics (IMEN), Universiti Kebangsaan Malaysia, 43600 UKM, Bangi, Selangor, Malaysia.

### Introduction

Optical receivers are used to detect optical power and to extract the information that is being transmitted. The incident optical power is detected by a photo detector, usually a PIN or avalanche photodiode (APD). A PIN or APD is an amplitude modulation envelope photo detector, insensitive to phase or small changes in wavelength. It generates an electrical output that reproduces the envelope of the received optical signal (Li, 2000). The most widely deployed photodiode for all lightwave applications is the PIN photodiode where its performance and characteristics are well understood and documented (Campbell, 1995).

Silicon PIN photodiodes is still in high demand for applications operating up until the 1100nm wavelength range. The emergence of the Fast Ethernet and Gigabit Ethernet require the usage of silicon photodiodes operating at a wavelength of 770-860nm. Applications requiring photodiodes in array form are also driving factors towards the development of silicon planar PIN photodiodes which can be fabricated and integrated with ease. The lowreliability and cost. high established manufacturability process make silicon an attractive material for the fabrication of a planar PIN photodiode (Li, 2000). The success in the development of silicon based PIN photodiodes provides a stepping stone towards the development of PIN photodiodes using III-V materials such as GaAs. InGaAs and InGaAsP.

## **PIN Photodiode Structures**

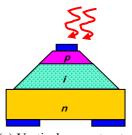

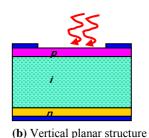

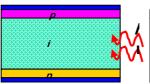

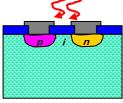

The structure of PIN photodiodes can be classified based on the location of the p, i and *n* regions arranged either vertically or in the same plane. A planar PIN photodiode is created in such a way that the p, i and nregions are all in one plane. Optical power is illuminated via the surface or the edge of the device. Figure 1(a)-(d) shows various structures of the PIN photodiode. The planar photodiode (PD) PIN has profound advantages compared to the vertical surface/edge illuminated PIN photodiode. Costly epitaxial layers are needed to form the p, i and n regions in a vertical structure using fabrication techniques such as MOCVD (*metalorganic chemical vapor deposition*) and MBE (*molecular beam epitaxy*). However, the planar PIN photodiode can be fabricated easily using standard CMOS processing techniques where the p and n regions are doped unto the substrate wafer using either diffusion or ion implantation techniques (Ehsan *et al.*, 2001).

with surface illumination

(a) Vertical mesa structure with surface illumination

(c) Vertical planar structure with edge illumination

(d) Planar structure with surface illumination

FIGURE 1 PIN photodiode structures

#### Theory

The current-voltage characteristic of a PIN photodiode with no incident light is similar to a rectifying diode. When the PIN photodiode is forward biased, as usual there is an exponential increase in the current. When a reverse bias is applied, a small reverse saturation current appears. It is related to the dark current as:

$$I_{D} = I_{SAT} \left( e^{\frac{qV_{A}}{k_{B}T}} - 1 \right)$$

(1)

where  $I_D$  is the PIN photodiode dark current,  $I_{SAT}$  is the reverse saturation current, q is the electron charge,  $V_A$  is the applied bias voltage,  $k_B=1.38 \times 10^{-23} \text{ J}^{/0}\text{K}$ , is the Boltzman Constant and T is the absolute temperature  $(273^{\circ}\text{K}=0^{\circ}\text{C})$ . Illuminating the photodiode with optical radiation, shifts the I-V curve by the amount of photocurrent  $(I_P)$ . Thus:

$$I_{TOTAL} = I_{SAT} \left( e^{\frac{qV_A}{k_B T}} - 1 \right) + I_P$$

(2)

where  $I_P$  is defined as the photocurrent as in equation 2. As the applied reverse bias increases, there is a sharp increase in the photodiode current. The applied reverse bias at this point is referred to as breakdown voltage. This is the maximum applied reverse bias, below which, the photodiode should be operated (also known as maximum reverse voltage).

The internal quantum efficiency for a photodiode is defined as the number of holeelectron pairs generated per photon. The external quantum efficiency is defined as the ratio of generated carriers to the number of incident photons within the device taking into consideration optical loss due to surface reflections, electrode shadowing and other geometrical characteristics. The external quantum efficiency is given by equation 3.

$$\eta = (1 - R) \cdot (1 - e^{-\alpha d}) \tag{3}$$

where d is the thickness of the absorption region, R is the reflectivity at the airsemiconductor interface. The total quantum efficiency is obtained by multiplying the internal and external quantum efficiencies respectively.

The responsivity of a photodiode is the ratio of generated electrical current to the incident optical power and is defined in terms of the device's external quantum efficiency. This is given by equation 4.

$$R = \frac{I_{opt}}{P_{opt}} = \left(\frac{q}{hv}\right)\eta_{ext} \quad [A/W] \quad (4)$$

The RC time constant for a photodiode is given by equation 5.

$$\tau_{RC} = \frac{1}{C_J (R_S + R_L)} \tag{5}$$

where  $C_J$  is the junction capacitance,  $R_S$  is the series resistance and  $R_L$  is the load resistance. The bandwidth is defined as:

$$f_{3dB} = \frac{1}{2\pi\tau_{RC}} \tag{6}$$

### **Materials and Methods**

### Simulation

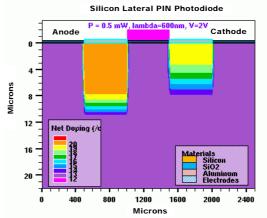

The silicon planar PIN photodiode device modeling and simulation was performed using Silvaco ATHENA and ATLAS simulation Silvaco Incorporated. softwares from ATHENA simulates semiconductor material processes based on two-dimensional physical structures built into a defined grid format and ATLAS solves differential equations derived from the Maxwell laws in each node of the grid in order to obtain electrical and optical characteristics of the device. Silicon with resistivity of 1000 ohms/cm<sup>2</sup> and <100>orientation was used as the substrate material. An oxide layer of 0.6µm thickness was deposited for masking purposes. Next. successive etch steps followed by diffusion were used to define the  $p^+$  and  $n^+$  wells. The  $p^+$ wells were formed by diffusing Boron for 120 minutes with a temperature of 1200° Celsius and a dose of 8.19 x  $10^{20}$  cm<sup>-3</sup>. The n<sup>+</sup> wells were formed by diffusing Phosphorous for 50 minutes with a temperature of 1000° Celsius and a dose of  $2.02 \times 10^{20} \text{ cm}^{-3}$ . After the oxide-etching step, Aluminum with thickness of 3µm was deposited and etched to form electrodes; anode  $(p^+ \text{ well})$  and cathode  $(n^+ \text{ well})$ well). The simulated device has an intrinsic region width, d varying from 0.5mm to 2mm with  $p^+/n^+$  well widths of 0.5mm.

## Fabrication

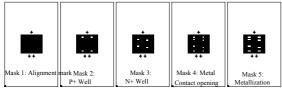

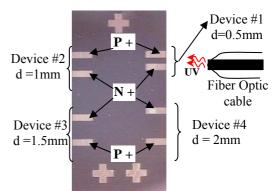

Fabrication of the device involves 28 steps. Each prototype contains four devices with different intrinsic region widths ie 0.5mm, 1.5mm and 2mm. The device 1mm, photomask was designed using AutoCAD and Adobe Illustrator software and the structure was transferred to negative and positive polymer plates coated with chromium by an outsource vendor. The photolithography process in the fabrication of the device involves 5 photomasks ie the alignment mark, p+ well window, n+ well window, metal contact wind.

N-type <100> silicon with resistivity of 1-1000 ohms/cm<sup>2</sup> and bulk concentration of 3.64 $x \ 10^{10}$  /cm<sup>3</sup> was used as the substrate material. Upon substrate cleaning the first photolithography was performed to transfer the alignment mark onto the substrate material using positive photoresist AZ 1500 from Clarient. A standard first spin speed of 800 rpm for 5 seconds and second spin speed of 4000 rpm for 30 seconds followed by softbake at 100 °C for 50 seconds was used to obtain a resist thickness of 0.5 µm.

Dash etchant solution was used to obtain a permanent marker on the substrate. After the etching and cleaning processes, dry oxidation using N<sub>2</sub> at 95 sccm and O<sub>2</sub> at 95 sccm for 240 minutes at 1200 °C was performed in order to obtain a diffusion masking oxide layer of 0.33µm. The second photolithography was carried out to obtain the p+ well openings. Spin-on diffusion technique using Boron B155 SOD from Filmtronics USA was utilized. Pre-diffusion first spin speed was at 400 rpm for 5 seconds and second spin speed was at 4000 rpm for 60 seconds. Next, hardbake at 200°C for 20 minutes was followed by drive-in at 1200 °C for 120 minutes.

Subsequent etching and oxidation processes is followed bv the third photolithography to create n+ wells using P509 SOD from Filmtronics USA. Prediffusion first spin speed was at 400 rpm for 5 seconds and second spin speed was at 4000 rpm for 60 seconds. Next, hardbake at  $200^{\circ}$ C for 20 minutes was followed by drive-in at 1000 °C for 50 minutes. The fourth photolithography was carried out to create metal openings and lastly the metal lift-off technique was utilized after the fifth photolithography process to obtain metal contacts on the device. Thermal evaporation furnace using e-gun was used to deposit Al for 45 seconds in order to obtain a metal layer thickness of 700 - 1200 Å. Annealing at 500 <sup>o</sup>C for 15 minutes was performed in a dry oxidation furnace with the flow of nitrogen gas N<sub>2</sub> at 2000 ml/min. Finally the device was cut and polished at the edges to allow for lateral illumination.

#### **Characterization**

The prototype was characterized for dark/photo I-V and responsivity utilizing the smart semi-automatic probing system from

Signatone and also *Metrics Interactive Characterization Software (ICS)* Version 3.5.0 at IMEN. The device was placed on a probing table while dark/photo I-V data was collected. Photo I-V data was obtained by illuminating the top of the device with red light ( $\lambda$ = 612nm) with three different optical powers; 0.2mW, 0.3mW and 0.5mW.

## Results

## Simulation Results

The current-voltage (IV), total quantum efficiency, responsivity, rise time and frequency response characteristics of the devices were simulated. The simulated structure for d=0.5mm is shown in Figure 2. The anode junction depth was at 11.2  $\mu$ m, p+ sheet resistance was 0.68 ohm/square (at X.value=750), intrinsic region sheet resistance was 1706.24 ohm/square(at X.value=1250) and n+ sheet resistance was at 12.62 ohm/square(at X.value=1750).

FIGURE 2 Si Planar PIN Photodiode (d=0.5mm) illuminated by optical beam

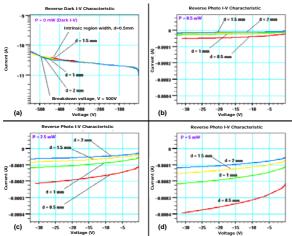

Figure 3(a)-(d) shows the reverse dark and photo I-V curves of the device for different intrinsic region widths. The breakdown voltage of -500V with equivalent dark current of 45.7pA was obtained for all the devices with different intrinsic region widths. Ideality factor of n=1, high dynamic resistance,  $(R_s =$  $10^6 \Omega$ ) and shunt resistances ( $R_D=10^{11} \Omega$ ) indicate that a ideal diode has been simulated. Illumination of the device with an optical spot power of P=0.5mW(V=-10V) generated an increased photocurrent in the devices  $(I_p = 0.038 \text{mA}).$ Increment in the incident optical power to P=2.5mW (I<sub>p</sub>=0.164mA) and P=5mW  $(I_p=0.314 \text{mA})$  increased the

photocurrent as well respectively. However, devices with a larger intrinsic region width showed lesser photocurrent increment for a fixed optical power intensity.

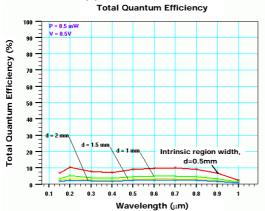

The total quantum efficiency,  $\eta$  of the devices peaked at a wavelength of 200nm at 10.2% for d=0.5mm, 5.13% for d=1mm, 3.41% for d=1.5mm and 2.54% for d=2mm where

FIGURE 3 Reverse dark and Photo I-V curves for devices with different intrinsic region widths and incident optical power (a) dark, (b) P=0.5mW, (c) P=2.5mW and (d) P=5 mW.

FIGURE 4 Total quantum efficiency for different intrinsic region widths.

increment in the intrinsic region width reduced the total quantum efficiency. The incident optical power was 0.5mW and applied reverse bias of 0.5V. This is shown in Figure 4.

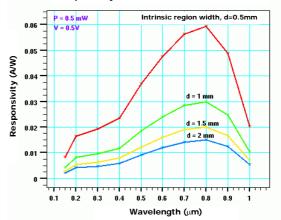

The responsivity curves are exhibited in Figure 5. The wavelength of the optical spot power was increased gradually from 150nm till 1000nm and responsivity values at each wavelength was extracted. The highest responsivity of 0.059 A/W at  $\lambda$ =800nm was achieved for the PIN photodiode device with

d=0.5mm. When the intrinsic region width is increased, the responsivity of the device decreased. This is due to the reduction in the generated photocurrent as a result of decreased electric field strength between electrodes which are placed further apart.

FIGURE 5 Responsivity of the devices with different intrinsic region widths

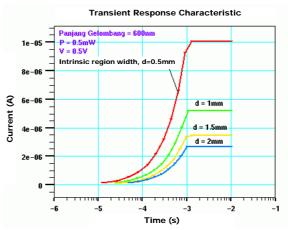

FIGURE 6 Rise time of the devices with different intrinsic region widths

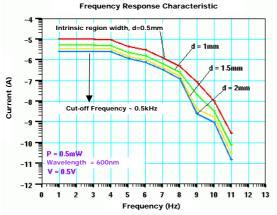

Fig 6 and Fig 7 shows the rise time and frequency response of the devices respectively with the same optical spot power (P=0.5mW) and reverse bias voltage (0.5V). Referring to Fig 7, the planar PIN photodiode with intrinsic region width of d=0.5mm shows the fastest rise time of 0.66ms which is equivalent to a bandwidth of 0.5kHz. The graph clearly shows a decrease in the final available photocurrent in the device when the intrinsic region width is increased. Rise time values calculated from values taken from the graph indicates an increase in the rise time when intrinsic region width is increased. This is because the electrons and holes formed in a wider intrinsic region need to travel further in

order to reach the electrodes. Fig 8 shows the frequency response of the planar PIN photodiode devices. The frequency response of the devices with larger intrinsic region width is lower. The rise time and frequency response of the devices are shown in Table 1.

FIGURE 7 Frequency response of photodiode devices with different intrinsic region widths

TABLE 1 Rise time and frequency response values of PIN photodiode devices with different intrinsic region widths

| Intrinsic<br>Region<br>Width<br>(mm) | Rise Time, t <sub>r</sub><br>(t <sub>90%</sub> - t <sub>10%</sub> )<br>(s) | f <sub>3dB</sub><br>(0.35/ t <sub>r</sub> )<br>(Hz) |

|--------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------|

| 0.5                                  | 6.6189 x 10 <sup>-4</sup>                                                  | 528                                                 |

| 1                                    | 7.0548 x 10 <sup>-4</sup>                                                  | 498                                                 |

| 1.5                                  | 7.2468 x 10 <sup>-4</sup>                                                  | 482                                                 |

| 2                                    | 7.7554 x 10 <sup>-4</sup>                                                  | 451                                                 |

#### Fabrication Results

Figure 8 shows the photomasks that were used and Figure 9 shows the fabricated device. Each prototype contains 4 devices each with different intrinsic region widths ie d=0.5mm, 1mm, 1.5mm and 2mm. The junction depth obtained for the p+ and n+ wells were 1.09 $\mu$ m and 1.61 $\mu$ m respectively. Bulk dopant concentration for the p+ and n+ wells were 8.19 x 10<sup>20</sup>/cm<sup>3</sup> and 2.02 x 10<sup>20</sup>/cm<sup>3</sup> respectively. The measured resistivity was 2.02 ohms/cm<sup>2</sup> and 5.07 ohms/cm<sup>2</sup> for the p+ and n+ wells respectively.

FIGURE 8 Device photomasks

FIGURE 9 Fabricated PIN photodiode

### Characterization Results

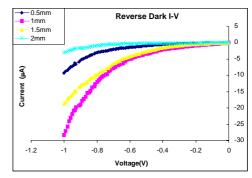

Figure 10 shows the reverse bias dark I-V data for all the four PIN photodiode devices. The trend is consistent with the trend obtained via simulation where increment in reverse bias current is observed when intrinsic region width is increased.

FIGURE 10 Reverse bias dark I-V

However, the breakdown voltage is extremely low at 0.8V at a reverse bias current of 0.77 $\mu$ A for device with d=2mm. Ideality factor approaching value of n=2, low dynamic resistance R<sub>s</sub> in the range of 167-868  $\Omega$  and low shunt resistance, R<sub>D</sub>=0.2-14 M $\Omega$  indicate the existence of generation-recombination currents in the prototype due to carrier tunneling through the intrinsic region.

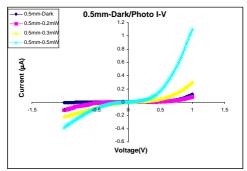

When the device is illuminated with three different optical powers ( $\lambda$ = 612nm, V=-0.2V); P=0.2mW, 0.3mW and 0.5mW, there is only slight increment in the device photocurrent as shown in Figure 11 where I<sub>p</sub> is 0.159µA, 13.4µA and 23.5µA respectively (for device with d=0.5mm). This is equivalent to a responsivity of 0.001 A/W ( $\eta=0.16\%$ ), 0.044A/W (η=9.05%) and 0.047A/W  $(\eta = 9.52\%)$ respectively. The small

photocurrent is due to the high leakage current in the device.

FIGURE 11 Dark/Photo I-V curve(d=0.5mm)

### Discussion

A silicon planar PIN photodiode was successfully modeled and simulated using Silvaco Athena and Atlas software. Intrinsic region width of the device was varied and the effect on device characteristics were analysed. Based on the obtained data, when intrinsic region width is increased, there is a decrease in the generated photocurrent, total quantum efficiency and responsivity. The device rise time increases and thus the bandwidth is reduced significantly. Prototypes of the simulated devices were fabricated using standard CMOS technology. Low breakdown voltage as well as ideality factor approaching a factor of 2 indicates the presence of leakage the device. High current in dopant concentration measurements in the intrinsic region of the device indicated that impurities have been deposited either due to insufficient substrate cleaning or thin oxide diffusion masking layer. Further investigation is required to identify the exact rootcause.

## Acknowledgements

The authors would like to acknowledge the support of the Malaysian Ministry of Science, Technology and Environment for sponsoring this work under IRPA grant No. 03-02-02-0069-EA231.

## References

Li, Ru (2000). Design and Development of High performance, monolithically integrated silicon-based optical receivers. Austin : The University of Texas. Campbell, J.C. (1995). Photodiodes for optoelectronic integrated circuits: Integrated Optoelectronics. San Diego: Academic Press.

Ehsan, A.A., Shaari, S., Majlis, B.Y.(2001) Silicon Planar p-i-n Photodiode for OEIC. *IEEE Nat'l. Symp. on Microelectronics*:316.

Schow, C.L. (1999). Development of high Speed monolithically integrated silicon optical receivers. Austin : The University of Texas.

Chang G., Kim Y., Lee J., Kang H. and Yi S. (2001). Design and Fabrication of a Si PIN photodetector with Peak Spectral Response in the red light for Optical Link. *J. of Microelectronics & Packaging Society*.8(1):1-4.

Menon P.S., Ahmad M. H. F., Tugi A., Ehsan A. A. and Shaari S. (2003). Dark Current-Voltage(I-V) Characteristic of a Silicon PIN Lateral Photodiode. *IEEE National Symposium on Microelectronics* : 207-210

Menon P.S. and Shaari S. (2003). The Effect of Intrinsic Region Width Variance on the Responsivity and Current-Voltage(IV) Characteristics of a Silicon Lateral PIN photodiode. *IMEN – Procs. on Photonics: Planar Waveguide and Fiber Based Opt. Comm.Dev.* 1: 76-79.