# DEVELOPMENT AND IMPLEMENTATION OF A NEW TECHNIQUE FOR BERT (BIT ERROR RATE TESTER) USING SDR PLATFORM

$\mathbf{BY}$

# **EKHLAS KADHUM HAMZA**

Thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

October 2011

## **DEDICATION**

# بِسْمِ اللَّهِ الرَّحْمَٰنِ الرَّحِيمِ

...قَالَ رَبِّ أَوْزِعْنِي أَنْ أَشْكُرَ نِعْمَتَكَ الَّتِي أَنْعَمْتَ عَلَيَّ وَعَلَىٰ وَالِدَيَّ وَأَنْ أَشْكُر نِعْمَتَكَ الَّتِي أَنْعَمْتَ عَلَيَّ وَعَلَىٰ وَالِدَيَّ وَأَنْ أَشْكُر نِعْمَتَكَ الَّتِي إِنِّي تُبْتُ إِلَيْكَ وَإِنِيِّ مِنَ الْمُسْلِمِينَ أَعْمَلَ صَالِحًا تَرْضَاهُ وَأَصْلِحْ لِي فِي ذُرِّيَّتِي إِنِيِّ تُبْتُ إِلَيْكَ وَإِنِيٍّ مِنَ الْمُسْلِمِينَ

سورة الأحقاف ﴿٥١﴾

Praise be to Allah, the most gracious and most merciful. Without his blessing and guidance, my accomplishments would never have been possible

MY supervisorAssoc. Prof.Dr.Widad Ismail

My beloved late parents for making out of me the person who can present such a work...for doing all this with pleasure.

My dearest sisters and brothers give me all their supports

#### ACKNOWLEDGMENT

"All praises and thanks to ALLAH"

Completing a doctoral dissertation is a very time consuming endeavour. I would not have been able to complete this research work without the assistance of the following people:

Associate Professor Dr.Widad Ismail for her encouragement, assistance, understanding and guidance throughout the period of my research. Ma, each day I looked up to you more as a sister and friend than a supervisor. Thank you so much for always being there for me.I would also like to appreciate Associate Professor Dr.Umi Kalthum for her assistance during my studentship. I would like to extend my gratitude to all members of staff of School of Electrical and Electronic Engineering, Universiti Sains Malaysia, who by one way or the other have contributed to the success of this work. I say a big thank you to you all. ALLAH will always be there for you in the time of your need. I also want to use this opportunity to express my gratitude and thanks to all members of staff of the Institute of Postgraduate Studies and Research Creativity and Management Office (RCMO) for providing postgraduate research grant scheme (USM –RU- PRGS), account no /1001/PELECT/8043005 for this work.

I would like to express my gratitude to all members of staff of the Technology University in Iraq: Special Professor. Dr.Kahtan K. KKazraji, Associate Professor Dr.Bassam G.Rasheed, Professor Dr.Ahamed A.Moosa, Professor Dr.Mohameed Salah, Associate Professor Dr.Dawwood, Professor Adawiya J.Hayder, Dr.Aboud Kreem, Mr.Ayaad, Mr.Allaa, Miss NourAdnan, Miss Rana and Miss Hind for their encouragement and cooperation. I also wish to express my

token of appreciation to the technical staff in CEDAC Lab USM, En. Shukri b.Korakkottil Kunhi Mohd and En.Hasnirol b.Baharom for their kind assistance during my test and experiment work. I would like to express my thanks to the technical staff in communication Lab who were very friendly and cooperative, En. Abdul Latip and Pn. Zammira bte. Khairuddin. The same appreciation goes to En. Zahir for his help. In addition, I would like to express my thanks to the editor of my thesis Miss Vinaand Mr. Mohammed Zubair for their efforts and help. I would also like to thank fellow students in the school of Electrical and Electronic Engineering, USM for their cooperation and hospitality. I specially want to appreciate Majed Sallal, Mohamed Elhefnawy, Girish Kumar, Wan Nur Hafsha, Mohamed Saeed, Chanuri, Farshed Eshghabadi and Mohamed Aboud. I would like to thank an Iraqi family in Malaysia, a person named Mr.Mohmeed and his mother for their assistant and support. Many thanks go to my best friend, classmate in degree, Hanan for her sisterly love and support. I would like to express my respect, honour and warmest thanks to all my dear family in Iraq, especially to my late parents, Hj. Kadhum Bin Hamza and Hjh. Mahdiah Binti Surayan, my dear sisters, Raja, Shamaa, Salma, Wafaa, Rehab, my dear brothers, Salman, Ghanam and Mohammed for their prayers, continuous support and true love showered upon me even though we are geographically thousand miles apart. In addition, many thanks go to my lovely nephew and niece, Hamza, Hadeel and Hallah. Finally, I would like to express my gratitude to the wonderful Malaysian people who gave their kindly help to me during my stay in Malaysia. Especially my best friend and sister from Malaysia: Nor Hayaty and her family. Thank you so much, I appreciate and love you all.

# TABLE OF CONTENTS

| DEL  | DICATI  | ON                               | ii    |

|------|---------|----------------------------------|-------|

| ACK  | KNOWI   | LEDGMENT                         | iii   |

| TAE  | BLE OF  | CONTENTS                         | v     |

| LIST | Γ OF TA | ABLES                            | X     |

| LIST | Γ OF FI | IGURES                           | xii   |

| LIST | ΓOF A   | BBREVIATIONS                     | xxi   |

| LIST | Γ OF SY | YMBOLSx                          | xviii |

| ABS  | STRAK   |                                  | xxix  |

| ABS  | STRAC   | Т                                | xxxi  |

| CHA  | APTER   | 1                                | 1     |

| INT  | RODUG   | CTION                            | 1     |

| 1.1  | G       | General View and Motivation      | 1     |

| 1.2  | Т       | Cools System Requirement         | 4     |

|      | 1.2.1   | SDR Hardware                     | 5     |

|      | 1.2.2   | SDR Software                     | 5     |

| 1.3  | P       | Problem Statement                | 6     |

| 1.4  | O       | Objectives of Thesis             | 6     |

| 1.5  | S       | cope and Limitations             | 7     |

| 1.6  | R       | Research Contribution            | 8     |

| 1.7  | S       | tructure of the Thesis           | 9     |

| CHA  | APTER   | 2                                | 12    |

| Back | kground | d and Literature Review          | 12    |

| 2.1  | In      | ntroduction                      | 12    |

| 2.2  | S       | oftware-Defined Radio Technology | 12    |

|     | 2.2.1     | Advantages and Disadvantages of Software-Defined Radios                                                      | 13          |

|-----|-----------|--------------------------------------------------------------------------------------------------------------|-------------|

|     | 2.2.2     | Critical SDR Components                                                                                      | 14          |

| 2.3 | Ex        | isting SDR Platforms                                                                                         | 20          |

|     | 2.3.1     | Universal Software Radio Peripheral (USRP)                                                                   | 20          |

|     | 2.3.2     | NICT SDR Platform                                                                                            | 21          |

|     | 2.3.3     | Berkeley Cognitive Radio Platform                                                                            | 21          |

|     | 2.3.4     | Kansas University Agile Radio (KUAR)                                                                         | 22          |

|     | 2.3.5     | Maynooth Adaptable Radio System                                                                              | 22          |

|     | 2.3.6     | LYRTECH                                                                                                      | 23          |

|     | 2.3.7     | WARP                                                                                                         | 23          |

|     | 2.3.8     | FLEX 3000                                                                                                    | 24          |

| 2.4 | Bit       | Error Rate Testing                                                                                           | 26          |

| 2.5 | Re        | lated Work                                                                                                   | 29          |

|     | 2.5.1     | BER Measurement-Based Software-Defined PlatformImplementation                                                | Radio       |

|     | 2.5.2     | DSP and FPGA-based Software-Defined Radio Implementation                                                     | 34          |

| 2.6 | Su        | mmary                                                                                                        | 54          |

| CH  | APTER 3   |                                                                                                              | 55          |

| Res | earch Rec | quirements and Proposed Methodology                                                                          | 55          |

| 3.1 | Int       | roduction                                                                                                    | 55          |

| 3.2 | Ba        | sic Infrastructure                                                                                           | 57          |

|     | 3.2.1     | SFFSDR Hardware                                                                                              | 58          |

|     | 3.2.2     | SFFSDR Software                                                                                              | 62          |

| 3.3 | Str       | ructure of the System                                                                                        | 66          |

|     | 3.3.1     | Proposed System Structure Description Based on the Simul-Hardware Co-Simulation and on Real-Time Approaches. | ation<br>68 |

| 3.4 | Su        | mmary                                                                                                        | 70          |

| CH   | APTER 4  | 1                                                                                                               | 71           |

|------|----------|-----------------------------------------------------------------------------------------------------------------|--------------|

| Proj | posed Sy | stem for FPGA Based on Simulation Approach                                                                      | 71           |

| 4.1  | In       | troduction                                                                                                      | 71           |

| 4.2  | De       | evelopment of the BERT test bench based on the FPGA Design for the                                              | he           |

|      | BI       | PSK Transceiver by Simulation Approach using Xilinx Blocks                                                      | 73           |

|      | 4.2.1    | BPSK Transmitter Design based on Xilinx Block                                                                   | 75           |

|      | 4.2.2    | BPSK Reciver Design Based on Xilinx Block                                                                       | 80           |

| 4.3  | De       | evelopment of FPGA for BFSK Transceiver based on Simulation Le                                                  | vel          |

|      | us       | ing Xilinx Blocks                                                                                               | 89           |

|      | 4.3.1    | FSK Transmitter based on Simulation Level using Xilinx Blocks                                                   | 91           |

|      | 4.3.2    | BFSK Receiver Design based on Xilinx Blocks                                                                     | 92           |

| 4.4  | De       | evelopment of FPGA Design for BPSK Transceiver based on Simula                                                  | ation        |

|      | Le       | evel using Xilinx and LyrtechBlocks                                                                             | 96           |

|      | 4.4.1    | The PSK Transceiver based on Simulation Level using Xilinx LyrtechBlocks                                        | and<br>97    |

|      | 4.4.2    | The FSK Transceiver based on Simulation Level using Xilinx Lyrtech Blocks                                       | and<br>103   |

| 4.5  | Si       | mulation Results and Analysis                                                                                   | .104         |

|      | 4.5.1    | Implementation Results of BPSK Transceiver based on FPGA a Xilinx System Generator and Lyrtech Blocks           | using<br>105 |

|      | 4.5.2    | Implementation Results of the FSK Transceiver based on FPGA taxilinx System Generator Blocks and Lyrtech Blocks | using<br>111 |

|      | 4.5.3    | BER Performance of the BPSK and FSK Digital Transceivers bon FPGA of Simulation Approach                        | ased<br>117  |

| 4.6  | Su       | ımmary                                                                                                          | .119         |

| CH   | APTER 5  | 5                                                                                                               | . 120        |

| Imp  | lementat | ion of the Proposed System based on FPGA using HIL Co-simulation                                                | ation        |

| Αŗ   | proach   |                                                                                                                 | . 120        |

| 5.1  | In        | troduction                                               | 120               |

|------|-----------|----------------------------------------------------------|-------------------|

| 5.2  | Sy        | stem Design of Digital Transceiver based on Hardware-in- | -the-loop         |

|      | (H        | IIL) co-simulation utilising SFFSDR Emulation            | 121               |

|      | 5.2.1     | PSK Transceiver based onHardware-in-the-loop (HIL)       | Co-simulation 123 |

|      | 5.2.2     | FSK Transceiver based onHardware-in-the-loop (HIL)       | Co-simulation 130 |

| 5.3  | FF        | PGA Co- Simulation Hardware Download based on Rapid      | Prototyping       |

|      |           |                                                          | 131               |

| 5.4  | Hi        | igh-Level Analysis and the SFFSDR Run                    | 134               |

| 5.5  | Su        | ımmary                                                   | 144               |

| CH.  | APTER 6   | 5                                                        | 145               |

| Proj | posed Sy  | stem based on Real-Time FPGA/DSPHardware Implement       | tation 145        |

| 6.1  | In        | troduction                                               | 145               |

| 6.2  | De        | evelopment Design of the BPSK and FSK Digital Transcei   | vers based on     |

|      | FF        | PGA / DSP                                                | 147               |

|      | 6.2.1     | DSP Design Part                                          | 147               |

|      | 6.2.2     | FPGA Design Part                                         | 151               |

|      | 6.2.3     | SFFSDR BERT Experimental Set-up                          | 153               |

|      | 6.2.4     | Significant Results                                      | 164               |

|      | 6.2.5     | Research finding and application                         | 172               |

| 6.3  | Su        | ımmary                                                   | 176               |

| CH   | APTER 7   | 7                                                        | 177               |

| Con  | clusion a | and Future Works                                         | 177               |

| 7.1  | Su        | ımmary and Conclusion                                    | 177               |

| 7.2  | Fu        | iture Works                                              | 179               |

| REI  | FERENC    | ES                                                       | 181               |

| APPENDIX A | 191 |

|------------|-----|

| APPENDIXB  |     |

| APPENDIX C | 198 |

| APPENDIX D |     |

| APPENDIX E |     |

| APPENDIX F | 237 |

# LIST OF TABLES

| Table 1.1:Signal Processing Complexity(Boccuzzi, 2008; Crockett, 1998)              |

|-------------------------------------------------------------------------------------|

| Table 2.1 : SDR Forum`s tier definitions (SDR)                                      |

| Table 2.2 : Advantages of Software-Defined Radio (Harrington, Hong, & Piazza,       |

| 2004)                                                                               |

| Table 2.3: The available Digital Signal Processing Devices (Rapaka et al., 2007) 19 |

| Table 2.4 : SDR RF Front-end Comparison Chart                                       |

| Table 2.9 : Comparison of the Related Works of this research                        |

| Table 3.1: Hardware and Software Requirements of this Work (Lyrtech, 2007) 57       |

| Table 3.2: Digital Processing Module Attributes                                     |

| Table 3.3: Data Conversion Module Attributes                                        |

| Table 3.4: RF Module Attributes                                                     |

| Table 4.1: Proposed Attributes of the BPSK Transceiver                              |

| Table 4.2: Summary of Specifications for Decimation of FIR Design                   |

| Table 4.3: Proposed Attributes of BFSK Transceiver                                  |

| Table 4.4: Summary Specification of FIR in Low-pass Filter, High-pass filter and    |

| Down Sampler Design96                                                               |

| Table 5.1 : Parameters used in the System Generator of the FPGA Configuration       |

| Block                                                                               |

| Table 5.2 : Parameters used in System Generator Block                               |

| Table 5.3: Device Utilisation Summary of Full Proposed System based on FPGA         |

| HIL Co-Simulation                                                                   |

| Table 5.4 : Timing Summary of Full Proposed System on FPGA HIL Co-Simulation        |

|                                                                                     |

| Table 5.5: FPGA Logic Utilisation and Logic Distribution (Map) based on HIL Co- |

|---------------------------------------------------------------------------------|

| Simulation                                                                      |

| Table 6.1: FPGA I/O Interfaces and corresponding MBDK FPGA Blocks               |

| Table 6.2: Timing Summary of Full Proposed System Based Real Time DSP / FPGA    |

| Hardware                                                                        |

| Table 6.3: FPGA Logic Utilisation and Logic Distribution (Map) based Real Time  |

| DSP / FPGA Hardware                                                             |

| Table 6.4: FPGA Logic Utilisation based placed and routed (PAR) based Real Time |

| DSP / FPGA Hardware                                                             |

| Table 6.5: Comparison of proposed BERT with related work                        |

# LIST OF FIGURES

| Figure 1.1: The Available Digital Signal Processing Devices(Safadi & Ndzi, 2006). 3  |

|--------------------------------------------------------------------------------------|

| Figure 1.2: The Small Form Factor SDR Development Platform is modular in design      |

| (Lyrtech, 2009)5                                                                     |

| Figure 1.3: Outline of the thesis                                                    |

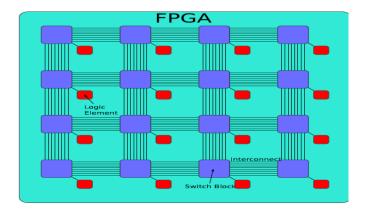

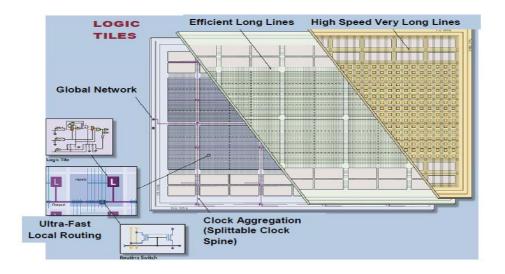

| Figure 2.1: Hardware Implementation Platforms for SDR                                |

| Figure 2.2: Simplified Version of FPGA Internal Architecture (Pietri, 2009) 18       |

| Figure 2.3: Typical FPGA Architecture (Peter, 2007)                                  |

| Figure 2.4: A Basic BER Measurement System (a) Loopback (b) End-To-End (Shah         |

| ,2006)                                                                               |

| Figure 2.5: FALCON Transceiver (Viebmann et al. 2006).                               |

| Figure 2.6: Test bed Set-up for Receiver Performance Evaluation (Xinyu, Bosisio,     |

| &Ke ,2006)                                                                           |

| Figure 2.7: Hardware Test Set-up. The Pulse-Based Transceiver was implemented on     |

| the FPGA board (Senguttuvan, Bhattacharya & Chatterjee ,2007) 33                     |

| Figure 2.8: SDR Test Bed of Experimental Set-up (Weiss et al.,2003)34                |

| Figure 2.9: Experimental setup for hardware co-simulatio of (Mannan, 2005) 36        |

| Figure 2.10: Software-Defined Radio Platform of (Fifield ,2006) Experiment 36        |

| Figure 2.11: Picture of the SDR Prototype of (Di Stefano, Fiscelli, & Giaconia 2006) |

| Experiment37                                                                         |

| Figure 2.12: DSP Set-up of (Di Stefano, Fiscelli, & Giaconia ,2006) Experiment 38    |

| Figure 2.13: SDR Platform. 39                                                        |

| Figure 2.14: KUAR Radio (Minden <i>et al.</i> ,2007)                                 |

| Figure 3.1: System Design Methodology                                                |

| Figure 3.2: CCS Development Environment (Texas .2001)                                |

| Figure 3.3: Mixing of Components from Simulink and Sysgen(Xilinx, 2008)         | . 65  |

|---------------------------------------------------------------------------------|-------|

| Figure 3.4: System Generator and Traditional Design Flows (Frigo et al., 2003)  | . 66  |

| Figure 3.5: Overview of the Simplified General Structure Block Diagram of the   |       |

| BERT Proposed System based on the Simulation and Hardware Co-                   |       |

| Simulation Approaches ( UPDATE)                                                 | . 67  |

| Figure 3.7: Overview of the General Block Diagram of BERT Proposed System       |       |

| based on Real-time distributed between FPGA and DSP( UPDATE)                    | . 67  |

| Figure 3.7: Block Diagram of a Generalised Feedback Shift Register with M-Stage | Э     |

| (Rappaport, 2002)                                                               | . 69  |

| Figure 4.1: Flow Chart of the Proposed System based on FPGA using Xilinx and    |       |

| LyrtechBlocks                                                                   | . 72  |

| Figure 4.2: Functional BPSK Transceiver Simulation Setup Diagram                | . 74  |

| Figure 4.3: Design of BPSK TransmitterSimulation Setup Diagram using System     |       |

| Generator for Hardware Implementation                                           | . 75  |

| Figure 4.4: PN Subsystem Design                                                 | . 76  |

| Figure 4.5: Screen Shot of PN Sequence Generator Subsystem designed in          |       |

| Simulink/Sysgen Environment.                                                    | . 76  |

| Figure 4.6: BPSK Modulation Subsystem Block                                     | . 77  |

| Figure 4.7: Screen shot of the BPSK Modulation Subsystem designed in Simulink   |       |

| /Sysgen Environment                                                             | . 78  |

| Figure 4.8: A Simplified View of the DDS Core                                   | . 80  |

| Figure 4.9: Design of BPSK Receiver Simulation Setup Diagram using System       |       |

| Generator for Hardware Implementation                                           | . 81  |

| Figure 4.10: BPSK Demodulation Subsystem Block                                  | . 82. |

| Figure 4.11: Screen shot of the BPSK Demodulation Subsystem designed in               |

|---------------------------------------------------------------------------------------|

| Simulink /Sysgen Environment                                                          |

| Figure 4.12 : Block Diagram for Multiple-Stage Decimation (Reed , 2002) 83            |

| Figure 4.13: Digital Filter Tolerance Scheme (Andreas, 1993)                          |

| Figure 4.14: Decimation Subsystem designed in Simulink/Sysgen Environment 85          |

| Figure 4.15: Filter Design Analysis Tool (FDAtool) Block                              |

| Figure 4.16: Generate Coefficients for the FIR Compiler                               |

| Figure 4.17: Settings of the Parameters for the Filter Design & Analysis Tool for the |

| Decimation of BPSK                                                                    |

| Figure 4.18: BERT Receiver Module                                                     |

| Figure 4.19: BERT Subsystem designed in Simulink/Sysgen Environment                   |

| Figure 4.20: Functional FSK Transceiver Simulation Setup Diagram using Xilinx         |

| Technology for Hardware Implementation                                                |

| Figure 4.21: Design of BFSK Transmitter Subsystem Simulation Setup Diagram            |

| using System Generator for Hardware Implementation91                                  |

| Figure 4.22: The BFSK Modulation Subsystem Block                                      |

| Figure 4.23: Screen shot of the BFSK Modulation Subsystem designed in Simulink        |

| /SysgenEnvironment                                                                    |

| Figure 4.24: Design of BFSK Receiver Subsystem Simulation Setup Diagramusing          |

| System Generator for Hardware Implementation                                          |

| Figure 4.25: The BFSK Demodulation Subsystem Block                                    |

| Figure 4.26: Screen shot of the BFSK Demodulation Subsystem designed in               |

| Simulink/Sysgen Environment                                                           |

| Figure 4.27: Decimation Subsystem of FSK Demodulation designed in Simulink            |

| /Sysgen Environment 95                                                                |

| Figure 4.28: (a) LPF Subsystem and (b) HPF Subsystem designed in             |

|------------------------------------------------------------------------------|

| Simulink/Sysgen Environment96                                                |

| Figure 4.29: Functional BPSK Simulation Setup Diagram designed in Simulink,  |

| Xilinx System Generator and Lyrtech Development Tools for Hardware           |

| Implementation                                                               |

| Figure 4.30: Design of BPSK Transmitter Simulation Setup Diagramusing System |

| Generator and Lyrtechblocks for Hardware Implementation98                    |

| Figure 4.31: DAC-A and DAC-B Blocks                                          |

| Figure 4.32: Design of BPSK Receiver Simulation Setup Diagram using System   |

| Generator and Lyrtechblocks for Hardware Implementation 100                  |

| Figure 4.33: ADC-A and ADC-B Blocks                                          |

| Figure 4.34: Function Block Parameters of Data Conversion Module             |

| Figure 4.35: Function Subsystem Block of down -Conversion Module             |

| Figure 4.36: Screen Shot of Down Converter Subsystem designed in Simulink    |

| /Sysgen Environment                                                          |

| Figure 4.37: Screen shot of I and Q Down Converter Subsystem designed in     |

| Simulink/Sysgen                                                              |

| Figure 4.38: Functional FSK Transceiver Simulation Setup Diagram designed in |

| Simulink, Xilinx System Generator and Lyrtech Development Tools for          |

| Hardware Implementation                                                      |

| Figure 4.39: Design of FSK Receiver Simulation Setup Diagram using System    |

| Generator and LyrtechBlocks for Hardware in ADC-A and ADC-B                  |

| Blocks                                                                       |

| Figure 4.40: Design of FSK Receiver Simulation Setup Diagram using System    |

| Generator and LyrtechBlocks for Hardware Implementation                      |

| Figure 4.41: Configuration of Simulation Run | 105 |

|----------------------------------------------|-----|

| Figure 4.42: Symbol Clock Signal             | 106 |

| Figure 4.43: PRBS Data Signal                | 106 |

| Figure 4.44: BPSK Modulation BB_I signal     | 106 |

| Figure 4.45: BPSK Modulation BB_Q signal     | 107 |

| Figure 4.46: BPSK Demod. Data Signal         | 107 |

| Figure 4.47:Delayed PRBS Data Signal         | 107 |

| Figure 4.48: Compare Signal                  | 108 |

| Figure 4.49: Symbol Clock Signal             | 108 |

| Figure 4.50: PRBS Data Signal                | 109 |

| Figure 4.51: BPSK Modulation BB_I signal     | 109 |

| Figure 4.52: BPSK Modulation BB_Q signal     | 109 |

| Figure 4.53: Down Conversionsignal to BB _I  | 109 |

| Figure 4.54: Down Conversionsignal to BB_ Q  | 110 |

| Figure 4.55: BPSK Demod. Data Signal         | 110 |

| Figure 4.56: Delayed PRBS Data Signal        | 110 |

| Figure 4.57: Compare Signal                  | 111 |

| Figure 4.58: Symbol Clock Signal             | 112 |

| Figure 4.59: PRBS Data Signal                | 112 |

| Figure 4.60: FSK Modulation BB_I signal      | 112 |

| Figure 4.61: FSK Modulation BB _Q signal     | 113 |

| Figure 4.62: FSK Demod. Data signal          | 113 |

| Figure 4.63: Delayed PRBS signal             | 113 |

| Figure 4.64: Compare Signal                  | 114 |

| Figure 4.65: Symbol Clock Signal             | 114 |

| Figure 4.66: PRBS Data Signal                                                |

|------------------------------------------------------------------------------|

| Figure 4.67: FSK Modulation BB _I signal                                     |

| Figure 4.68: FSK Modulation BB _Q signal                                     |

| Figure 4.69: Down Conversionsignal toBB _I                                   |

| Figure 4.70: Down Conversionsignal toBB _Q                                   |

| Figure 4.71: FSK Demod. Data Signal                                          |

| Figure 4.72: Delayed PRBS                                                    |

| Figure 4.73: Compare Signal                                                  |

| Figure 4.74: Simulated BER versus theoretical BER of BPSK Transceiver 118    |

| Figure 4.75: Simulated BER versus theoretical BER of FSK Transceiver         |

| Figure 5.1: MATLAB/Simulink and Hardware Co-Simulation (Shirazi & Ballagh,   |

| 2003)121                                                                     |

| Figure 5.2: Flow Chart of Proposed System based on HIL Co-Simulation         |

| Figure 5.3: Screen shot of top view of the PSK Receiver implementation using |

| Simulink and Xilinx System Generator based on HIL for Hardware               |

| Implementation                                                               |

| Figure 5.4: AWGN Simulink Block                                              |

| Figure 5.5: Dialogue Box of AWGN Channel Simulation Block                    |

| Figure 5.6: BPSK Transceiver Subsystem to be translated into Bitstream       |

| Figure 5.7: FPGA Configuration Dialogue Box for the SFF SDR Development      |

| Platform                                                                     |

| Figure 5.7: System Generator Block Dialogue Box for the SFF SDR Development  |

| Dlatform 128                                                                 |

| Figure 5.9: Screen shot of top view of the FSK Receiver implementation using |  |  |

|------------------------------------------------------------------------------|--|--|

| Simulink and Xilinx System Generator based on HIL for Hardware               |  |  |

| Implementation                                                               |  |  |

| Figure 5.10: FSK Transceiver Subsystem to be translated into Bitstream       |  |  |

| Figure 5.11: Generation Complete Message                                     |  |  |

| Figure 5.12: HIL Co-Simulation Library for BPSK and FSK Transceivers         |  |  |

| Figure 5.13: BPSK and FSK Transceiver HIL Co-Simulation Model                |  |  |

| Figure 5.14: Downloading Bitstream of BPSK and FSK Transceiver to SFFSDR     |  |  |

| Development Platform. 134                                                    |  |  |

| Figure 5.15: FPGA HIL Co-Simulation Test Bed Setup for SFFSDR Development    |  |  |

|                                                                              |  |  |

| Figure 5.15: FPGA Device Utilisation                                         |  |  |

| Figure 5.17:Modulation-Demodulation Process (Results of BPSK Transceiver     |  |  |

| obtained by SFFSDR Development Platform) a. Symbol Clock, b. PRBS            |  |  |

| Data @ 1 MHz, c , d, BPSK Modulation BB_I and BB-Q signals ,e.               |  |  |

| Demodulated Data, f. Delayed PRBS Data, g. Signals comparison 14             |  |  |

| Figure 5.18:Modulation-Demodulation Process (Results of FSK Transceiver      |  |  |

| obtained by SFFSDR Development Platform) a. Symbol Clock, b. PRBS            |  |  |

| Data @ 1 MHz, c , d, FSK Modulation BB_I and BB-Q signals ,e.                |  |  |

| Demodulated Data, f. Delayed PRBS Data, and g. Signalscomparison             |  |  |

|                                                                              |  |  |

| Figure 5.18: Measured BER of BPSK Transceiver based on FPGA (HIL) Co-        |  |  |

| simulation versus Theoretical and Simulated BER                              |  |  |

| Figure 5.19: Measured BER of FSK Transceiver based on FPGA (HIL) Co-         |  |  |

| simulation versus Theoretical and Simulated BER                              |  |  |

| Figure 6.1: The Design Flow of FPGA/DSP based on Development Platform 146       |

|---------------------------------------------------------------------------------|

| Figure 6.2: The Top Model Design of FPGA/DSP                                    |

| Figure 6.3: DSP Link of the Specific Platform Model                             |

| Figure 6.4 : Configuration Parameters Dialogue Box, Solver Parameters           |

| Figure 6.5: Configuration Parameters Dialogue Box, Real-Time Workshop           |

| Parameters. 150                                                                 |

| Figure 6.6: Functional BPSK Transceiver Simulation Set-up Diagram for Real-Time |

| DSP/FPGA Hardware                                                               |

| Figure 6.7: Functional BPSK Transceiver Simulation Set-up Diagram for Real-Time |

| DSP/FPGA Hardware                                                               |

| Figure 6.8: Measurements of BERT Experimental Set-up                            |

| Figure 6.9: Block Diagram of Environment Setup Connections                      |

| Figure 6.10: Setting Parameters of the injected noise                           |

| Figure 6.11: Spectra of the RF module transmitter. The module is programmed 402 |

| MHz                                                                             |

| Figure 6.12: Generating Bitstream                                               |

| Figure 6.13: DSP Building Process                                               |

| Figure 6.14: Simulink of DSP Building Process                                   |

| Figure 6.15: Executables Created Successfully                                   |

| Figure 6.16: Connect to Target Button                                           |

| Figure 6.17: BER Display on DSP Module                                          |

| Figure 6.18: Spectra of the RF module (span 1 MHz) transmitter for proposed     |

| system transmission at 1 MHz data rate                                          |

| Figure 6.19: IF output spectra of the DCM for forproposed system                |

| Figure 6.20: IF output spectra of the DCM for proposed system with 1 MHz random  |  |  |

|----------------------------------------------------------------------------------|--|--|

| data                                                                             |  |  |

| Figure 6.21: BPSK intermediate quadrature and in-phase components (IF-Q and IF-  |  |  |

| I) at the output of the DCM / DAC                                                |  |  |

| Figure 6.22: FSK modulated Intermediate Frequency quadrature and in-phase        |  |  |

| (FSK-I & FSK-Q) components at the output DCM / DAC                               |  |  |

| Figure 6.23: PSK modulated signal at the output of RF module at IFof 30 MHz. 163 |  |  |

| Figure 6.24: FSK modulated signal at the output of RF module at IF of 30 MHz.164 |  |  |

| Figure 6.25: BER performance measurements of the theoretical, simulation, HIL    |  |  |

| co-simulation and real time results of BPSK digital transceiver based            |  |  |

| SFFSDR platform                                                                  |  |  |

| Figure 6.26: BER performance measurements of the theoretical, simulation, HIL    |  |  |

| co-simulation and real time results of FSK digital transceiver based             |  |  |

| SFFSDR platform170                                                               |  |  |

## LIST OF ABBREVIATIONS

1G First Generation

2G Second-Generation

2.5G Two and Half Generation

3G Third Generation

4G Fourth- Generation

ACI Adjacent Channel interference

ACLR Adjacent Channel Leakage Ratio

ADC Analogy digital converter

AM Amplitude Modulation

ANC Active Noise Control

ASK Amplitude Shift Keying

ASICs Application Specific Integrated Circuits

AGC Automatic Gain ControL

AWGN Additive White Gaussian Noise

BER Bit error rate

BERT Bit Error Rate Tester

BPSK Phase Shift Keying

BTS Based Transceiver Station

CCStudio Code Composer Studio

CDMA Code Division Multiple Access

CLT Central Limit Theorem

CPE Customer-Premises Equipme

CPH A control processor host

CPLD Complex Programmable Logic Device

CPU Central Processing Unit

CSMA- Carrier Sense Multiple Access With Collision Detection

CA

CVSD Continuously Variable Slope Delta Modulation

DB Digital Board

DCS Digital Cellular System

DECT Digital Enhanced Cordless Telecommunication

DAC Digital-to-Analogue Converters

DP Development Platform

DRP Digital Receiver Processor

DSPs Digital Signal Processors

DSL Digital Subscriber Lines

DSSS Direct – Sequence Spread spectrum

DVB Digital Video Broadcasting

DUT Design under Test

EHF Extremely High Frequency

EIRP Effective Isotropic Radiated Power

ELF Extremely Low Frequency

EMI Electromagnetic Interference

EMIF External Memory Interface

ENR Excess Noise Ratio

EVM Error Vector Magnitude

FDL Fiber Delay Line

FDATool Filter Design Analysis Tool

FETs Field-Effect Transistor

FHSS Frequency-HoppingSpread Spectrum

FIFO First-In- First-Out

FIR Finite Impulse Response

FM Frequency Modulation

FSK Frequency Shift Keying

FPGAs Field Programmable Gate Arrays

GPPs General-Purpose Processors

GSM Group Special Mobile

GPON Gigabit-Capable Passive Optical Network

GMSK Gaussian Minimum Shift Keying

HR Hardware radio

HDL Hardware Description Language

HIL Hardware-in-the-loop co-simulation

HF High Frequency

HW/SW Hardware/Software

IC Integrated Circuits

IEEE Institute of Electrical and Electronics Engineers

ISR Ideal software radio

IF Intermediate Frequency

IIR Filters Infinite Impulse Response Filters

I/O Input/output

IQ In-phase and Quadrature

IMT-2000 International Mobile Telecommunications 2000

IP Internet Protocol

ISE Integrated Software Environment

IS-95 Interim Standard 95

ISM Industrial, Scientific, & Medical Radio Frequency Band

ITU International Telecommunication Union

JTRS Joint Test Action Group

KUAR Kansas University Agile Radio

LA Link Adaptation

LF Low Frequency

LPF low-Pass Filter

MAC Medium Access Control

MADs Number of Multiples and Adds

MAI Multiple Access Interference

MARS Maynooth Adaptable Radio System

MBDK Model-Based Design Kit

MC Modulation Classification

MDS Minimum Detectable Signal

MDA Model Driven Architecture

MF Medium Frequency

MGT Multi-Gigabit Transceiver

MILCOM Military Communications

MI Modulation Index

ML Maximal Length

MODEM Modulation – Demodulation

MSK Minimum Shift Keying

NICT Institute of Information and Communications Technology

NP Network Processors

OFDM Orthogonal Frequency Division Multiplexing

OOK On-Off Keying

OPB On-Chip Peripheral Bus

QPSK Quadrate Phase Shift Keying

$\pi/4$  QPSK  $\pi/4$  Differential Quadrate Phase Keying

OMG Object Management Group

OSI Open Systems Interconnection model

QAM Quadrature Amplitude Modulation

QoS Quality of Service

PCS Personal Communication Services

PDC Personal Digital Cellular

PHY Physical layer

PLL Phase Locked Loop

PM Phase modulation

PN Pseudo-Random Noise

PRBS Pseudo-Random Bit Sequence

PR Partial Reconfiguration

RAM Radar-Absorbing Material

RBP Reprogrammable Baseband Processor

RF Radio Frequency

RFPWM RF Pulse Width Modulator

RISC Reduced Instruction Set Computer

ROM Read Only Memory

RTOS Real-time Operating Systems

SD Secure Digital

SD Sphere Decode

SSB Single Sideband

SDR Software Defined Radio

SFF Small Form Factor

SFF SDR Small Form Factor SDR Evaluation Module/ Development

EVM/DP Platform

SNR Signal-to-Noise Ratio

$SNR_{req}$  SNR required

SHF Super High Frequency

SLF Super Low Frequency

SCR Software controlled radio

SPI Serial Peripheral Interconnection

SR Software Radio

TETRA Terrestrial Trunked Radio

TDMA Time Division Multiple Access

TRF Tuned Radio Frequency

UCS Universal Signal Classifier

UHF Ultra High Frequency

ULF Ultra Low Frequency

UMTS Universal Mobile Telecommunications System

USB Universal Serial Bus

USRP Universal Software Radio Peripheral

VHF Very High Frequency

VLF Very Low Frequency

VLIW Very Long Instruction Word

VOAs Variable Optical Attenuators

VCO Voltage Controlled Oscillator

VPBE Video Processing Back-End

VPFE Video Processing Front-End

VPSS Video Processing Subsystem Protocol

v4 Xilinx virtex 4

v5 Xilinx virtex 5

VSB Vestigial sideband modulation

WARP Wireless Open-Access Research Platform

WCS Wireless Communications Systems

WCDMA Wideband Code Division Multiple Access

W-LAN Wireless Local Area Network

W-PAN Wireless Personal Area Network

XST Xilinx Synthesis Technology

# LIST OF SYMBOLS

$E_b$  Bit Energy  $N_o$  Noise Power

Pe Error Probability  $P_R$  Received Power  $P_T$  Transmitter Power  $P_R$  Received Power  $P_R$  No value

# PEMBANGUNAN DAN IMPLEMENTASI SATU TEKNIK BARU UNTUK BERT (BIT ERROR RATE TESTER) MENGGUNAKAN SDR PLATFORM

#### **ABSTRAK**

Pendekatan rekabentuk sepunya (perkakasan / perisian) menjadi pilihan menawarkan kemampuan masa nyata sambil memberikan berprospek kerana penyelesaian fleksibel yang merangkumi peningkatan sistem yang kompleks dan masa-untuk-pasaran. Rekabentuk Hybrid GPP / DSP / FPGA adalah penyelesaian yang layak untuk teknologi perisian radio ditakrifkan. Tesis ini menunjukkan rekabentuk yang praktikal dan prosedur pelaksanaan untuk membina model yang bermanfaat, cekap dan fleksibel dari kesalahan bit error rate tester (BERT) pada lapisan fizikal untuk UHF-band dari penghantar/penerima digital dengan menggunakan arkitektur baru di Radio Multi-Core Software-Defined platform. Sebuah BERT untuk penerima digital adalah melibatkan pemodelan saluran pemancar dan bising serta penerima itu sendiri. Secara tradisional BER dinilai menggunakan simulasi, yang sangat memakan masa dan tidak diautomasi dalam masa nyata. Untuk mengatasi masalah ini, tesis ini menyajikan skim untuk ujian BER dalam menggunakan SFFSDR dengan beberapa perintah nilai pemecutan Penyelidikan besarnya dibandingkan. ini menyajikan pembangunan penghantar/penerima digital yang dicadangkan pada platform SFFSDR dalam tiga langkah. Langkah pertama ialah tahap simulasi yang menggunakan Xilinx System Generator blok dan blok Lyrtech. Langkah kedua melibatkan rekabentuk Simulasi Co Hardware-(HIL) pelaksanaan pada perkakasan alat pemodelan FPGA. Langkah Ketiga menggambarkan rekabentuk berdasarkan Real Time DSP / FPGA perkakasan. Implementasi yang dicadangkan mempunyai penjana nombor rawak sebagai sumber

data. Data ini dimodulasi dan ditukar ke atas sebelum disuapkan ke modul RF SDR SFF. Isyarat yang diterima daripada RF yang kemudian ditukar ke bawah dan dan disuapkan ke komparator yang menghitung jumlah kesalahan didemodulasi dengan membandingkannya dengan bit dihantar. Dua skim modulasi koheren (iaitu FSK dan BPSK ) untuk pelaksanaan ini secara nyata. digunakan disaranka agar prototaip perkakasan hibrid termasuk kedua-dua blok DSP dan FPGA secra bersama adalah platform perkakasan yang ideal untuk melaksanakan sistem. Pendekatan yang dicadangkan BERT meminimumkan keperluan perkakasan "custom" dan sistem ujian dengan mengintegrasikan fungsi jalur asas pada FPGA menggunakan SFFSDR. FPGA memberikan gabungan berprestasi modul isyarat dan berprestasi logik tinggi berkonfigurasi besar yang pemprosesan menghasilkan satu platform sesuai fabrik untuk prototaip sistem komunikasi. BER pendekatan dalam masa nyata telah diuji untuk berkesan pada digital BPSK dan FSK yang diperolehi berada dalam urutan 10<sup>-3</sup> pada SNR 15 dB dan 17dB bagi setiap satu.

# DEVELOPMENT AND IMPLEMENTATION OF A NEW TECHNIQUE FOR BERT (BIT ERROR RATE TESTER) USING SDR PLATFORM

### **ABSTRACT**

Hardware/Software (HW/SW) co-design approaches become prospective choice due to its real time operation since these solutions are so flexible that cover extensive complicated systems and reduce time from design to market. Hybrid digital signal processors (DSPs), field programmable gate arrays (FPGAs) and general-purpose processors (GPPs) designs are viable solution for software defined radio (SDR) technology. This thesis demonstrates a practical design and implementation procedure for building a useful, efficient and flexible model of a bit error rate tester (BERT) on physical layer for UHF-band of the digital transceivers by using new architecture in Multi-Core Software-Defined Radio Platform. A BERT for a digital receiver involves modelling a transmitter and noisy channel, as well as the receiver itself. Typically, BER is calculated using simulations, which are very timeconsuming and not automated in real time. In order to solve this problem, this thesis presents a scheme for BER testing using small form factor (SFF) SDR. This research presents the development of the proposed digital transceiver on the SFFSDR platform in three steps. The first step is the simulation level, which uses the Xilinx System Generator block and Lyrtech block. The second step involves the design of the Hardware-in-the-loop (HIL) Co-simulation and the implementation on FPGA hardware-modeling tool. The third step describes the design based on Real Time DSP/ FPGA hardware. The proposed implementation has a random number generator as data source. This data is modulated and up-converted before it is fed to the RF module of the SFFSDR .The received signal from the RF is later downconverted and demodulated and fed to the comparator which calculates the number

of errors by comparing it with the transmitted bits. Two types modulation (i.e. FSK and BPSK) are used to test proposed for real implementation. It is suggested that a hybrid hardware prototype including including both the DSP blocks, and FPGA together as an ideal hardware platform for implementing the system. The proposed BERT approach minimizes the need for custom hardware and test systems by integrating the baseband functionalities on FPGAs using SFFSDR. FPGAs provide a mix of high-performance dedicated signal processing modules and a large reconfigurable logic fabric, which makes them suitable platform for prototyping communication systems. The developed BERT is tested successfully for BPK and FSK digital transceivers with BER obtained to be in the order of 10<sup>-3</sup> at SNR of 15dB and 17dB respectively.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 General View and Motivation

The emergence of wireless communications is developing at an alarming pace and this has brought about the practice of new standards and protocols in the field of communications. Rapid implementation of the wireline-based Internet has led to the demand for wireless Internet connectivity but with added capabilities, such as integrated services that offer seamless global coverage and user-controlled quality of service (QoS). The challenge in inventing advance wireless Internet connectivity is assembled by the desire for future-proof radios, which keep radio hardware and software from becoming obsolete as new standards, techniques, and technology become addressable (Reed, 2002; Srikanteswara et al., 2000; Tuttlebee, 2004). Thus, this motivated the concept of a software-defined radio (SDR). This means that the digital-to-analogue and analogue-to-digital conversions perform as close as possible to the radio frequency. By implementing modulation, demodulation, channel coding and other required processing tasks in the software, the aim of extending the digital domain is achieved (Bonnet et al., 2000; Jian et al., 2000). Therefore, users, service providers and manufacturers become more independent of the realisation of one specific data transmission standard, since by downloading appropriate software code, a different functionality can be adopted by the communications system. Re-using the same software and reconfigurable hardware to handle different processing algorithms would enable an efficient, flexible alternative to current prototyping and implementation methods (Gonzalez et al., 2009; Weiss et al., 2003).

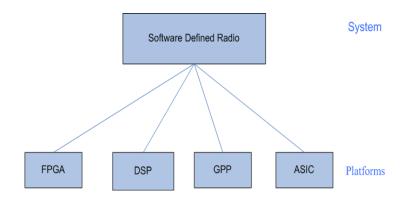

As hybrid solutions verify a radio's potential and implementation, they are essential mechanisms for the operation and design of software radios. Since radio operations use programmable designs running on digital hardware, there is flexibility in implementing different wireless standards and waveforms. Hybrid solutions are available in various forms on single-chip custom integrated circuits (ICs), of which the most commonly used for software radio are digital signal processors (DSPs), field programmable gate arrays (FPGAs), general-purpose processors (GPPs), and application specific integrated circuits (ASICs). Hybrid GPP/DSP/FPGA architecture is a viable solution for the software- defined radio technology (Blume, Hubert, Feldkamper *et al.*, 2009).

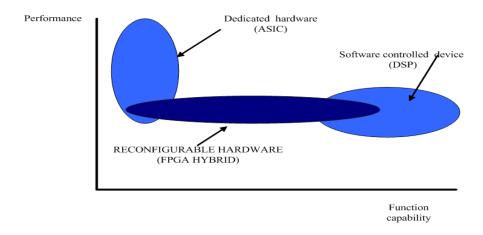

Figure 1.1 shows the available digital signal processing devices (Safadi & Ndzi, 2006). Analysing the trade-offs among these options and determining the best digital hardware solution for a software radio system is a complex and challenging task for system designers. Some of the main factors in design composition of digital hardware of software radio are computational power, computational density, hardware flexibility, application flexibility, power consumption, reconfiguration time and the total cost involved, each of which providing varying levels of reprogrammability and performance (Reed, 2002; Zhang ,2008). Even though DSPs are less flexible they are often used to provide more deterministic implementation when compared to languages such as C/C++. FPGAs also offer better performance but require specialised programming tools and knowledge, which reduces their flexibility. Despite the ASIC offering the most optimised and efficient digital hardware implementation, their design is in fixed silicon with little or no flexibility(Farrell, 2009; Hee Kong et al., 2006; Thabet et al., 2009).

Figure 1.1: The Available Digital Signal Processing Devices(Safadi & Ndzi, 2006)

With the recent advent of software-defined radio (Mitola, 1995), wireless communication systems have become applicable solutions to a wider range of challenging applications. However, the different computational complexities of wireless communication standards requirements are as shown in Table 1.1(Boccuzzi, 2008; Crockett, 1998).

Table 1.1:Signal Processing Complexity(Boccuzzi, 2008; Crockett, 1998).

| Wireless standard | Approximate computational complexity |

|-------------------|--------------------------------------|

|                   | (MIPS)                               |

| 802.11 a&b        | 9000                                 |

| WCDMA             | 9000                                 |

| IS-95             | 500                                  |

| GPRS              | 300                                  |

| GroupeSpeciale    | 100                                  |

| Mobile (GSM)      |                                      |

The feasibility of the SDR based implementation BERT (bit error rate tester) of the wireless digital modem on Multi-Core Software-Defined Radio Platform is studied in this thesis. In fact, this platform, called small form factor (SFF) SDR development platform, was a joint development between Texas Instruments

(TI), Xilinx and Lyrtech as well as a host of leading software tool vendors. Bit error rate (BER) and noise figure will be the main parameters used in measuring the noise. BER characteristic is one of the basic measures of the performance of any digital communication system. BER is the fundamental measurement used when testing receiver performance parameters such as sensitivity and selectivity(Ismail, 2003). It is the percentage of erroneous bits received compared to the total number of bits received during an observation period. As the Signal/Noise ratio decreases gradually, for example, the BER increases suddenly near the noise level where l's and 0's become confused. BER shows whether the system is dead or alive. Traditionally, BER is evaluated using code simulations, which are very timeconsuming. To overtake these problems, this thesis presents a scheme for BER testing BPSK & FSK digital transceivers in FPGAs based on SFF SDR. BPSK is chosen for SFFSDR prototype because of its ability to tolerate low SNR values, as well as its simplicity, which is reflected in its low cost implementation. In this research, FSK is used in the implementation of wireless transceiver. FSK can be found in many low-cost, such as cordless phones, wireless audio speaker systems and RF consumer telemetry systems.

#### **1.2** Tools System Requirement

During the work of this thesis, hardware and software requirement have been used to complete the tasks of building a BER tester of wireless modem-based SFFSDR. Following is a description of the SDR hardware and programs used and a description of their purpose.

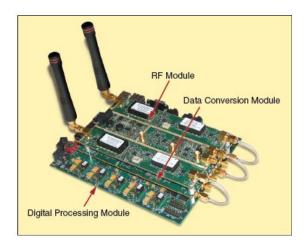

### 1.2.1 SDR Hardware

The SDR hardware uses the SFF SDR DP manufactured by the Canadian-based company Lyrtech as shown in Figure 1.2 (Lyrtech, 2009). The platform is a development platform for radio applications and not used in production. It is a standalone device and consists of three major modules, each controllable by software instructions. This platform is designed as low-cost, off-the-shelf, integrated hardware and software development solutions, and packs some of the latest DSP (DM6446) and FPGA (virtex\_4SX35) technology. It has various interfaces on the board, such as RS-232 serial port, 10/100 Mbps Ethernet port, universal serial bus (USB) port, and secure digital (SD) memory card slot. Unfortunately, until today the USB port and the SD memory card slot are not supported (Details of this hardware is in Chapter 3).

Figure 1.2: The Small Form Factor SDR Development Platform is modular in design (Lyrtech, 2009)

## 1.2.2 SDR Software

This Platform supports Lyrtech Advanced Development Platform Software, which requires MATLAB, Xilinx System Generator and Xilinx ISE. (Details of this software are in Chapter 3).

### 1.3 Problem Statement

One important measure of system reliability is the BER of a coding scheme for communication in the presence of noise. A BER tester for a digital receiver involves modelling a transmitter and noisy channel, as well as the receiver itself. As modern systems often require extremely reliable communication (e.g. error probability, P<sub>e</sub> on the order of  $10^{-10}$ ), this means that a tester must process billions of symbols (or more) over a wide range of signal-to-noise ratios (SNR). Using traditional HDL and software simulations often requires days or weeks to obtain a BER curve (bit error rate as a function of SNR) for a single set of parameters for a decoder (e.g. code rate and trace back length). Simulations are generally not suitable for the evaluation of communication systems with a low BER. Therefore in order to overcome these problems, this research demonstrates how such tools can be used to build a bit error rate tester (BERT) hardware accelerators in FPGA linked to Simulink using System Generator, and also how HIL co-simulation and Real Time DSP / FPGA hardware of the entire system SFFSDR provide a high speed-up over a pure software simulation. Thus, there is a need for a practical design and implementation procedure for building a useful, efficient and flexible model of BERT on physical layer of the digital transceivers.

## 1.4 Objectives of Thesis

The aim of this research is to build a useful, efficient and flexible model of BERT that will be implemented in real time. This tester is developed to evaluate the bit error rate of digital baseband modem in wireless communication systems. The process of building is achieved by the rapid prototyping approach-based on SFFSDR platform that combines both hardware and software environments. The key features

of the introduced models are low complexity, low power consumption and efficient data transmission. The objectives of this research are summarised as shown below:

- 1- To design and develop Frequency Shift Keying(FSK) and Binary Phase Shift Keying (BPSK) based wireless communication transceiver by employing Xilinx System Generator blocks and Lyrtech SFFSDR models.

- 2- To integrate and implement a new approach of BERT design for the developed BPSK and FSK transceiver on SFFSDR development platform based on the simulation and HIL co-simulation, and Real Time DSP / FPGA hardware approaches.

- 3- To test and verify the proposed configuration to ascertain the repeatability and reliability of the proposed model and technique.

- 4- To analyse and compare the performance of propsed model for BER measurement.

### 1.5 Scope and Limitations

The scope of this present work is focused in designing and implementing BERTs for the digital transceiver on high-level simulation and to develop a prototype system on the SFFSDR board. This required the design and development of simulation program and experimental set up that could verify and validate the success of the proposed model and technique. This model and technique would later be developed and integrated on real time SFFSDR development platform. BERTs are actually used to evaluate the bit error rate of the digital modem in wireless communication systems. The BERTs that were developed are illustrated using simulation, HIL co-simulation and real-time on the SFFSDR development platform.

The BERT based Real Time DSP / FPGA Hardware on the Virtex-4 SX35 FPGA application is carried out and the BER performance results evaluated.

One of the major limitations involving this study is the research development time consumed in the learning of the System Generator blocks, ISE suiteneeded to design a fully functional transceiver. In addition, each algorithm used in the simulation has to be tested independently before being integrated into a communication system. Interconnection of different algorithm blocks must be tested to ensure proper operation with neighbouring blocks. Another limitation is with respect to the FPGA, which can only support the fixed-point operation but not the floating point. Therefore, the conversion from floating point to fixed-point using the fix-point arithmetic has to be carried out. The DSP and FPGA clock frequencies are 594MHz and 125 MHz, respectively. The process of normalizing the speeds is a tedious process and the verification step of the proposed system has to undergo numerous steps before it can be finalized. The bandwidth of the signal had to be limited to 20 MHz (Lyrtech, 2009).

### 1.6 Research Contribution

This research presents many attractive characteristics and also several contributions to the current state of information knowledge. The general and positive contributions include the following:

This was the first attempt to develop a combination of Simulink and Xilinx ISE based SFFSDR to design BERT system. A new technique for BERT design and FPGA implementation based on Multi-Core Software-Defined Radio platform for different digital transceiver systems were attempted. It showed how the Model-Based Design could be applied in the development of the SFFSDR platform leading to the development of component models of the physical system. It was shown that the use

of DSP blocks could significantly reduce the number of logic elements, which can be used to further expand system functionalities. This research demonstrated the practicality of the design flow for Hybrid GPP/DSP/FPGA architecture for software-defined radio technology. Soft-core design was incorporated into the hardware to reduce the logic elements. The proposed implementation of Pseudo-Random Bit Sequence (PRBS) patterns as data source provided a convenient way of testing the high-speed interfaces, and is mainly used for BER. The performance comparisons of different modulation and demodulation techniques in SFFSDR implementation were carried out. For telemetric applications, PSK was considered efficient form of data modulation, providing the lowest probability of error for a given received signal level during the measurement of over one symbol period.

The transmitter and receiver systems design were carried out using three different modes. BPSK and FSK system using Xilinx System Generator Blocks and the Lyrtech SFFSDR models were proposed for system level simulation. HIL co-simulation models for transceiver of the FSK and BPSK system were used to validate certain portions of FPGA algorithms on actual hardware.

The real-time implementation of the transceiver for FSK and BPSK system and the distribution of the SDR modem components between the DSP core and the FPGA were implemented.

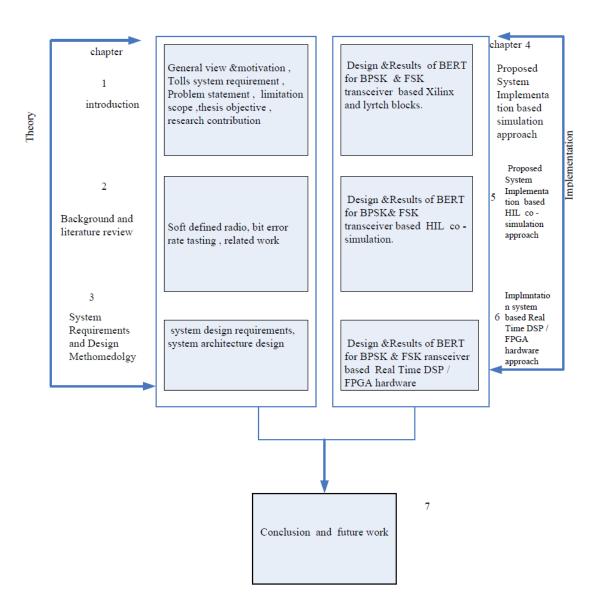

#### 1.7 Structure of the Thesis

The outline of this work is shown in Figure 1.3. It is divided in two major parts: theory and implementation. The first few chapters cover the theoretical parts while the later chapters describe the work and the results.

**Chapter 1** presents a brief introduction on the role of the reconfigurable solutions for implementing the sophisticated signal processing tasks in the digital communication

systems, with emphasis on the tasks performed by the digital transverse-based SFFSDR. This chapter also presents the objective, contribution of thesis and tools environment requirement.

**Chapter 2** introduces the topic by giving a general survey about the related subjects in the design; an overview of SDR concept, followed by DSP and FPGA related topics, BERT and related work.

A more detailed description of the requirements of the proposed communication system design and methodology design is introduced in **Chapter 3.**

**Chapter 4** presents the design implementation and results-based simulation level. **Chapter 5** presents the design implementation and results-based HIL co-simulation level.

**Chapter 6** presents the design implementation and results-based Real Time DSP / FPGA hardware.

Finally, the conclusions made from this research are presented in **Chapter 7**.

Figure 1.3: Outline of the thesis

### **CHAPTER 2**

# **Background and Literature Review**

### 2.1 Introduction

The aim of this chapter is to provide theories, information and previous work about certain topics, which are needed for the design and implementation of this research. The key to understanding these high-level requirements that drive the radio specifications are the various waveforms the radio intends to support. A general description of Next Generation Receiver Architectures (Software-Defined Radio Technology) is introduced. A description of the Embedded Signal Processing, ASIC, DSP, GPP and FPGA is also presented. In addition, BERT theory and its related work to this research are presented.

## 2.2 Software-Defined Radio Technology

Due to recent increase in demand from wireless communications to IC designers, the trend now is to design extremely flexible receivers that can support multiple standards. The SDR concept has evolved over the past three or four decades, with applicability to various parts of a radio. A software-defined radio is a system, which uses software for modulation and demodulation of communication signals. The goal is to use as little hardware as possible(Schmid, *et.al.* 2006). The SDR Forum has developed a multi-tiered definition of SDR by establishing five tiers encompassing different categories of software radio systems. The five-tier concept is summarised in Table 2.1. Tier 0 represents the 'traditional' radio hardware and forms a baseline reference. The uppermost tier, Tier 4, represents the 'ultimate' vision of SDR. Reality falls somewhere in the middle. For most applications, state-of-the-art

SDR currently aligns with Tier 2 definition. Note that, as mentioned above, it may be argued that virtually all modern wireless communication equipment may be classified as being software-controlled radios (i.e., Tier One) (Alsliety & Aloi, 2007; Chen *et al*, 2010).

Table 2.1 : SDR Forum's tier definitions (SDR)

| . Implement all the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | the    |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| changes in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |  |  |  |  |

| functionality require physical intervention to implement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |  |  |  |  |

| Multiple HRs is required to support several frequencies and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |  |  |  |  |