# DEVELOPMENT OF SPACER FREE SELF-ALIGNED CONTACT IMPLANTATION FOR POWER DEVICES

BANU A/P POOBALAN

UNIVERSITI SAINS MALAYSIA 2009

### DEVELOPMENT OF SPACER FREE SELF-ALIGNED CONTACT IMPLANTATION FOR POWER DEVICES

by

### **BANU A/P POOBALAN**

Thesis submitted in fulfillment of the requirements for the degree of Master of Science

November 2009

### DECLARATION

I declare that this is a result of my own research and does not contain any materials previously published, written or produced by another person except where due reference is made in the text. All the sources in this thesis are totally PRIVATE and CONFIDENTAL.

| Sign             | : |  |

|------------------|---|--|

| Candidate's Name | : |  |

| Date             | : |  |

|                  |   |  |

|                  |   |  |

| Witness          | : |  |

| Witness<br>Sign  | : |  |

|                  | : |  |

#### ACKNOWLEDGEMENT

The author would like to express her appreciation for the contributions of several people for their spontaneous support, which helped her to complete the research report successfully.

First and foremost, the author would like to extend her sincere thanks to the project supervisors Dr. Resch Roland and Ir Dr Cheong Kuan Yew for sharing their invaluable advice and expertise in executing the research. Their encouragement and valued constructive criticisms are very much appreciated. The author is also indebted to the supervisors for spending their precious time proofreading and verifying the accuracy of the content in this report.

The author also would like to express her sincere gratitude to her mentor Mr Ung Boon Hoe for his extensive knowledge and infinite guidance thought out the completion of the research. Special gratitude is also given to the CoolMOS team for giving the author positive feedback thought out the completion of the research.

The author also wish like to take this opportunity to tremendously acknowledgement all the relevant Infineon staffs especially the Operation, Production, Technology and Quality department staffs for their direct and indirect support and help. The author is greatly appreciates Infineon Malacca and Munich team for performing the back end characterization and qualification on the samples.

Heartfelt thanks to Univeriti Sains Malaysia (USM) for giving her the opportunity to be a part of this research and enabling her to carry out this project. The author's also indebted to Infineon Technology, Kulim for funding the research and allowing the author to experience the actual workplace of a wafer fabrication company. Last but not the least, the author wishes to thank her friends and family members for always being there and offering suggestions for improvement.

### **TABLE OF CONTENTS**

|     |        |                         | Pag                | ge  |

|-----|--------|-------------------------|--------------------|-----|

| AC  | KNOW   | LEDGEMENT               |                    | i   |

| TA  | BLES O | F CONTENTS              | i                  | iii |

| LIS | T OF T | ABLES                   |                    | vi  |

| LIS | T OF F | GURES                   | V                  | /ii |

| LIS | T OF A | PPENDICES               | 2                  | xv  |

| LIS | T OF S | MBOLS AND ABBR          | <b>EVIATIONS</b> x | vi  |

| ABS | STRAK  |                         | X                  | ix  |

| ABS | STRAC  | ſ                       | 2                  | XX  |

| CH  |        |                         |                    |     |

|     |        | 1 INTRODUCTION          |                    | 1   |

| 1.1 | ·      | ct Introduction         |                    | 1   |

| 1.2 |        | em Statement            |                    | 4   |

| 1.3 | 5      | ctives                  |                    | 7   |

| 1.4 | -      | e of the Project        |                    | 8   |

| 1.5 | Outl   | ne of the thesis        |                    | 10  |

| СН  | APTER  | 2 LITERATURE REV        | VIEW               |     |

| 2.1 | Intro  | uction                  | 1                  | 11  |

| 2.2 | Cool   | AOS Basics              | 1                  | 11  |

|     | 2.2.1  | Structure               | 1                  | 11  |

|     | 2.2.2  | Principles of Operation | ı 1                | 13  |

|     |        | 2.2.2.1 On State        | I                  | 13  |

|     |        | 2.2.2.2 Off State       | 1                  | 15  |

|     | 2.2.3  | Static Characteristics  | 1                  | 15  |

|     |        | 2.2.3.1 On resistance   | e 1                | 15  |

|     |        | 2.2.3.2 Breakdown       | Voltage 1          | 18  |

|     |        | 2.2.3.3 Transconduc     | tion               | 19  |

|     |        | 2.2.3.4 Threshold vo    | ltage              | 20  |

|     |        | 2.2.3.4 Dynamic cha     | racteristics 2     | 20  |

|     |        | 2.2.3.5 Switching be    | haviour 2          | 22  |

|     | 2.2.3.6 Device Ruggedness                                      | 24 |

|-----|----------------------------------------------------------------|----|

|     | 2.2.3.7 Applications                                           | 26 |

| 2.3 | Spacer                                                         | 28 |

|     | 2.3.1 Spacer Fabrication                                       | 28 |

|     | 2.3.2 Spacer Function                                          | 30 |

| 2.4 | Polysilicon oxide fabrication and function                     | 33 |

| 2.5 | Undoped Silica Glass layer (USG) and Borophosphosilicate Glass | 36 |

|     | (BPSG)                                                         |    |

|     | 2.5.1 USG and BPSG deposition                                  | 37 |

| 2.6 | Ion Implantation and Diffusion on the Source region            | 38 |

|     | 2.6.1 P++ implantation and diffusion on the source region      | 38 |

|     | 2.6.2 Arsenic implantation and diffusion on the source region  | 40 |

|     | 2.6.3 Ion implantation on misalignment contact hole overlay    | 41 |

# **CHAPTER 3 PORJECT METHODOLOGIES**

| 3.1 | Project | Methodologies Introduction                                | 42 |

|-----|---------|-----------------------------------------------------------|----|

| 3.2 | Standar | d Process Flow of Spacers Block and Subsequence Processes | 45 |

| 3.3 | Concep  | t 1 Description                                           | 47 |

|     | 3.3.1   | First Concept- Design of Experiment 1 (a)                 | 48 |

| 3.4 | Secon   | d Concept Description                                     | 51 |

|     | 3.4.1   | Second Concept- Design of Experiment 2(a)                 | 53 |

|     | 3.4.2   | Second Concept- Design of Experiment 2(b)                 | 56 |

|     | 3.4.3   | Second Concept- Design of Experiment 2(c)                 | 58 |

| 3.5 | Third   | Concept Description                                       | 61 |

|     | 3.5.1   | Third Concept -Design of Experiment 3 (a)                 | 62 |

|     | 3.5.2   | Third Concept -Design of Experiment 3 (b)                 | 65 |

|     | 3.5.3   | Third Concept -Design of Experiment 3 (c)                 | 68 |

|     | 3.5.4   | Third Concept -Design of Experiment 3(d)                  | 71 |

|     | 3.5.5   | Third Concept -Design of Experiment 3(e)                  | 75 |

|     | 3.5.6   | Third Concept -Design of Experiment 3(f)                  | 77 |

|     | 3.5.7   | Third Concept -Design of Experiment 3(g)                  | 80 |

|     | 3.5.8   | Back end Characterization                                 | 83 |

# **CHAPTER 4 RESULTS AND DISCUSSIONS**

| 4.1 | Projec   | t Results Introduction                        | 85  |

|-----|----------|-----------------------------------------------|-----|

| 4.2 | First C  | Concept                                       | 86  |

|     | 4.2.1    | First Concept- Design of Experiment 1 (a)     | 86  |

| 4.3 | Second C | Concept                                       | 90  |

|     | 4.3.1    | Second Concept Design of Experiment 2(a)      | 90  |

|     | 4.3.2    | Second Concept -Design of Experiment 2(b)     | 96  |

|     | 4.3.3    | Second Concept- Design of Experiment 2(c)     | 99  |

| 4.4 | Third Co | oncept                                        | 105 |

|     | 4.4.1    | Third Concept-Design of Experiment 3(a)       | 105 |

|     | 4.4.2    | Third Concept- Design of Experiment 3(b)      | 108 |

|     | 4.4.3    | Third Concept-Design of Experiment 3(c)       | 110 |

|     | 4.4.4    | Third Concept -Design of Experiment 3(d)      | 114 |

|     | 4.4.5    | Third Concept -Design of Experiment 3(e)      | 119 |

|     | 4.4.6    | Third Concept -Design of Experiment 3(f)      | 122 |

|     | 4.4.7    | Third Concept -Design of Experiment 3(g)      | 125 |

|     | 4.4.8    | Third Concept –Back end Characterization 3(g) | 131 |

| CH  | APTER 5  | CONCLUSION AND RECOMMENDATIONS                |     |

| 5.1 | Summary  | У                                             | 137 |

| 5.2 | Recomm   | endation                                      | 140 |

| REI | FERENC   | ES                                            | 141 |

| LIS | T OF PU  | BLICATIONS                                    | 146 |

| API | PENDICE  | ES                                            | 147 |

#### LIST OF TABLES

| Tables | s No.                                                                                                                            | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------|------|

|        | Table shows conditions of Temperature, Oxidation time, $O_2$ flow, $H_2$ flow and HCI flow for 500nm and 250nm polysilicon oxide | 48   |

- 4.1 Table shows for reference group (a) threshold voltage for various 132 drain current and temperature (b) break down voltage for various temperature(c) transconduction for various temperature (d) on drain current for various temperature (d) drain to source voltage for various forward current and various temperature (f) on resistance for various gate to source voltage and various temperature at drain current =13.1A (g) on resistance for various gate to source voltage and various temperature at drain current =20.7A

- 4.2 Table shows for spacer free target group (a) threshold voltage for various drain current and temperature (b) break down voltage for various temperature(c) transconduction for various temperature (d) on drain current for various temperature (d) drain to source voltage for various temperature (e) drain to source voltage for various forward current and various temperature (f) on resistance for various gate to source voltage and various temperature at drain current =13.1A (g) on resistance for various gate to source voltage and various temperature at drain current =20.7A

- 4.3 Table shows capacitance series which includes Ciss, Rg , Q ,Coss 134 and Crss

- 4.4 Table shows avalanche energy single pulse, avalanche 135 energy repetitive and avalanche current repetitive for the reference specification

## LIST OF FIGURES

| Figur | Figures No.                                                                                                                                      |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

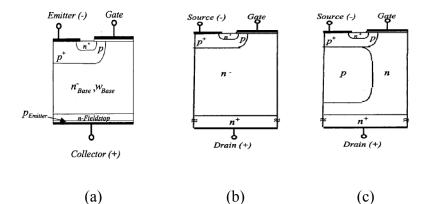

| 1.1   | Cross section of conventional (a) Field-stop IGBT, (b) D-MOSFET and (c) CoolMOS                                                                  | 3  |

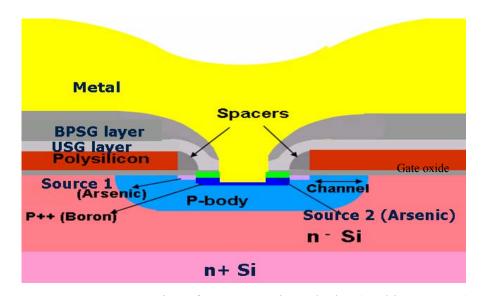

| 1.2   | Cross section of power transistor device                                                                                                         | 4  |

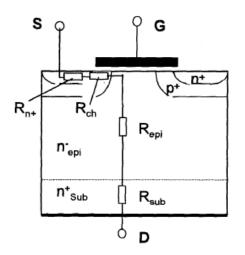

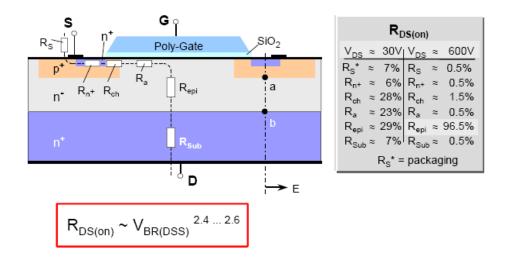

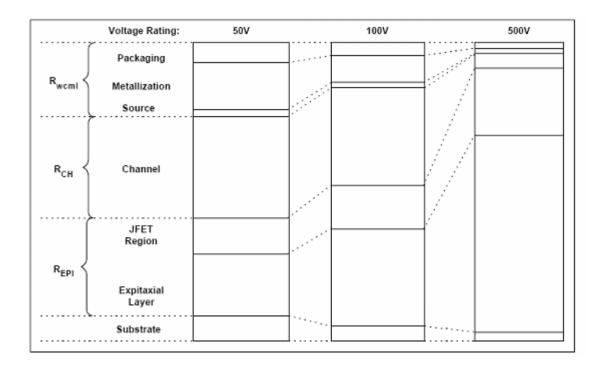

| 2.1   | State of the art 600 V-MOSFET with series of resistance                                                                                          | 13 |

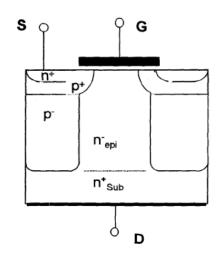

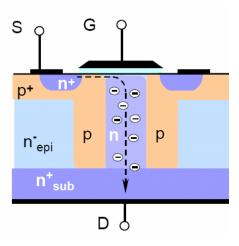

| 2.2   | Cross Section of a 600V- CoolMOS with p-n columns                                                                                                | 13 |

| 2.3   | Electrons flow from the source of the CoolMOS high voltage power MOSFET.                                                                         | 14 |

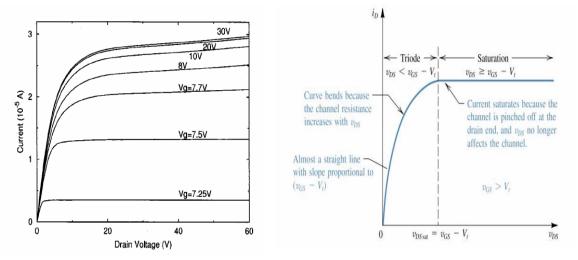

| 2.4   | Output characteristics of the CoolMOS transistor                                                                                                 | 14 |

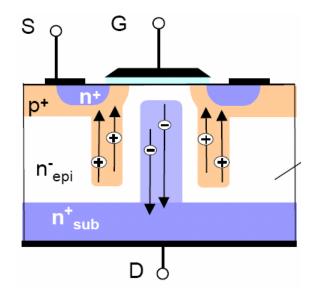

| 2.5   | Current flow during turn-off in a CoolMOS device                                                                                                 | 15 |

| 2.6   | Components of the overall RDs(on) in conventional power<br>MOSFETs for low and high voltage devices.                                             | 16 |

| 2.7   | Relative contributions to Rds(on) with different voltage ratings                                                                                 | 17 |

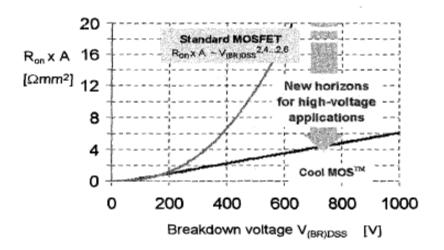

| 2.8   | COOLMOS technology offers a linear relationship between<br>blocking voltage and on-resistance                                                    | 19 |

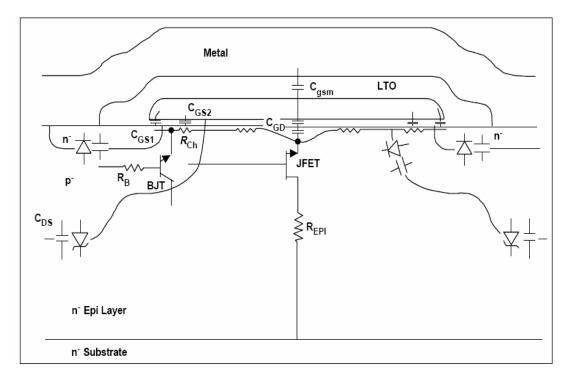

| 2.9   | Power MOSFET Parasitic Components                                                                                                                | 21 |

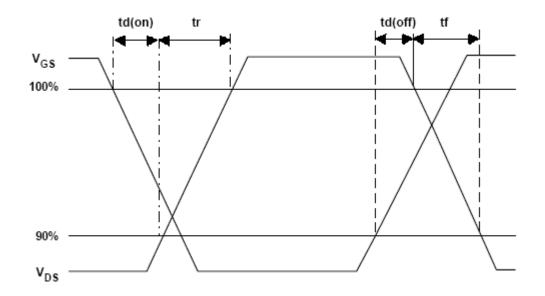

| 2.10  | Switching Time Test VGs and VDs Waveforms                                                                                                        | 22 |

| 2.11  | Gate Charge Test, (b) Resulting Gate and Drain Waveforms                                                                                         | 23 |

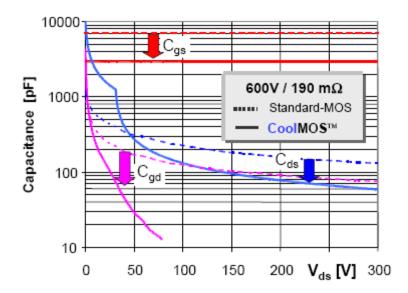

| 2.12  | CoolMOS offers a substantial reduction of gate-source and "Miller" capacitance, $C_{GS}$ and $C_{GD}$ respectively, as well as a very favourable | 24 |

| 2.13                                | Equivalent circuit of power MOSFET showing possible mechanisms for dv/dt Induced Turn-on                                                                                                                                                                                                                                          | 26             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.14                                | Flyback is the most common topology for power supplies with less<br>than 250W. The integrated combination of a CoolMOS and a<br>control-IC (CoolSETTM) allows cost effective solutions with a<br>minimum number of components                                                                                                     | 27             |

| 2.15                                | (a) TEOS based oxide deposition (b)Cross section shows spacers formation                                                                                                                                                                                                                                                          | 28             |

| 2.16                                | Power DMOSFET cross section after (a) gate definition and p-base formation, (b) the formation of shallow surface p+-diffused region                                                                                                                                                                                               | 29             |

| 2.17                                | Conventional power DMOSFET cell with a deep-diffused p+ region to reduce the p-base sheet resistance and its contact resistance.                                                                                                                                                                                                  | 32             |

| 2.18                                | Cross sections of DMOSFET unit cells illustrating a reduction in<br>cell size by incorporating a shallow surface p+ diffusion shown in<br>(b) in place of a conventional deep-diffused p+ region as shown in<br>(a)                                                                                                               | 32             |

| 2.19                                | Fabrication process of polysilicon oxide                                                                                                                                                                                                                                                                                          | 33             |

|                                     |                                                                                                                                                                                                                                                                                                                                   | 55             |

| 2.20                                | Diagram of USG and BPSG deposition.                                                                                                                                                                                                                                                                                               | 37             |

| <ul><li>2.20</li><li>2.21</li></ul> | Diagram of USG and BPSG deposition.<br>Cross-section view of the DMOS portion of the n-channel IGBT,<br>showing the counterdoped channel together with the integral p+ short                                                                                                                                                      |                |

| 2. 21                               | Cross-section view of the DMOS portion of the n-channel IGBT,                                                                                                                                                                                                                                                                     | 37             |

| 2. 21                               | Cross-section view of the DMOS portion of the n-channel IGBT,<br>showing the counterdoped channel together with the integral p+ short<br>The flow chart shows the summarized overall experiments which have                                                                                                                       | 37<br>39       |

| 2. 21<br>3.1                        | Cross-section view of the DMOS portion of the n-channel IGBT,<br>showing the counterdoped channel together with the integral p+ short<br>The flow chart shows the summarized overall experiments which have<br>been performed for Concept 1, Concept 2 and Concept 3<br>Portion of the Standard Process Flow of Spacers Block and | 37<br>39<br>44 |

| 3.5  | Figure shows the conditions of gas curve of process gasses during polysilicon oxidation                                                                                                                                                                                          | 49 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6  | The portion of the process flow that shows the polysilicon oxide formation via oxidation process                                                                                                                                                                                 | 51 |

| 3.7  | The figure shows the evaluation performed for the Second Concept to investigate the USG side wall thickness and spacer thickness with various P++ implantations energy                                                                                                           | 52 |

| 3.8  | The portion of the process flow that shows the USG deposition 300 nm with various $P$ ++ implantations energy                                                                                                                                                                    | 55 |

| 3.9  | The portion of the process flow that shows the anisotropic plasma etching of 250 nm spacer width, followed by P++ implantation and other subsequence process                                                                                                                     | 57 |

| 3.10 | The portion of the process flow that shows the USG deposition 320 nm / 400 $$ nm and various P++ implantations energy                                                                                                                                                            | 60 |

| 3.11 | The figure shows the evaluation performed for Concept 3 in which $P++$ is implanted into contact hole                                                                                                                                                                            | 61 |

| 3.12 | The portion of the process flow that shows the variation on source 1 implantation with other conditions remained as STD                                                                                                                                                          | 64 |

| 3.13 | The portion of the process flow that shows the variation on source 2 implantation with other conditions remained as STD                                                                                                                                                          | 67 |

| 3.14 | The portion of the process flow that shows the variation on P++<br>annealing conditions after being implanted into contact hole vs the<br>STD condition with P++ implantation through spacers                                                                                    | 70 |

| 3.15 | The portion of the process flow that shows the P++ implantation into contact hole, skipped spacer block, skipped source 2, skipped annealing condition 900°C, 30min during the TEOS oxide deposition vs the STD condition with P++ implantation through spacer, skipped source 2 | 74 |

| 3.16 | The portion of the process flow that shows the P++ implantation into misaligned contact hole with resist , skipped spacer block, skipped source 2, skipped spacer block, skipped source 2, skipped annealing condition 900°C, 30min during the TEOS oxide deposition             | 76 |

ix

| 3.17 | The portion of the process flow that shows the various P++<br>implantations into contact hole without resist/ with resist, skipped<br>spacer block, skipped source 2,skipped annealing conditions 900°C,<br>30min during the TEOS oxide deposition                                                                         | 79 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.18 | The portion of the process flow that shows the P++ implantation into contact hole without resist/ with resist, skipped spacer block, skipped source 2, skipped annealing condition 900°C, 30min during the TEOS oxide deposition                                                                                           | 82 |

| 4.1  | Figures show the cross section of polysilicon oxide thickness ~ 233 nm                                                                                                                                                                                                                                                     | 86 |

| 4.2  | Figures show the cross section of polysilicon oxide thickness ~ 558 nm (a) left side view (b) full view                                                                                                                                                                                                                    | 87 |

| 4.3  | The figures show simulation result (a) 900°C, 60.5 minutes (b) 900°C, 150.5 minutes (c) STD condition: 900°C, 30 minutes + 900 °C, 60 minutes of source 1 (arsenic) diffusion profile                                                                                                                                      | 88 |

| 4.4  | Figures show the cross section of USG layer thickness ~ 300 nm (a) full view (b) right view                                                                                                                                                                                                                                | 90 |

| 4.5  | Figures show the cross section of standard condition (spacer + USG layer thickness ~300 nm) (a) left view (b) full view                                                                                                                                                                                                    | 91 |

| 4.6  | The figures show simulation result of Boron implantation on top of 300 nm USG layer (a) 80 keV, $5 \times 10^{15}$ cm <sup>-2</sup> ; 100 keV, $5 \times 10^{15}$ cm <sup>-2</sup> ; 120 keV, $5 \times 10^{15}$ cm <sup>-2</sup> and Boron implantation with spacers (b) STD: 60 keV, $5 \times 10^{15}$ cm <sup>-2</sup> | 92 |

| 4.7  | The figures shows the experiment result of threshold voltage for<br>boron (P++) implantation on top of 300 nm USG layer with various<br>implantations energy (80 keV ~120 keV) and boron (P++)<br>implantation without spacers (60 keV)                                                                                    | 94 |

| 4.8  | The figures shows the experiment result of on resistance for boron (P++) implantation on top of 300 nm USG layer with various implantations energy (80 keV~120 keV) and boron (P++) implantation without spacers (60 keV)                                                                                                  | 94 |

| 4.9  | The figures shows the experiment result of transconductance for boron (P++) implantation on top of 300 nm USG layer with various implantations energy (80 keV $\sim$ 120 keV) and boron (P++)                                                                                                                              | 95 |

implantation without spacers (60 keV)

| 4.10 | The figures shows the experiment result of drain to source current<br>for boron (P++) implantation on top of 300 nm USG layer with<br>various implantations energy ( $80 \text{ keV} \sim 120 \text{ keV}$ ) and boron (P++)<br>implantation without spacers ( $60 \text{ keV}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | Figures show the cross section of (a) left view of STD spacer width $\sim$ 420 nm (b) left view of spacers overetched $\sim$ 250 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 96  |

| 4.12 | The figures shows experiment result of threshold voltage for boron (P++) implantation with STD spacers and spacers overetched to 250 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97  |

| 4.13 | The figures shows experiment result of on resistance for boron (P++) implantation with STD spacers and spacers overetched to 250 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98  |

| 4.14 | The figures shows experiment result of transconduction for boron (P++) implantation with STD spacers and spacers overetched to 250 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98  |

| 4.15 | The figures show simulation results of boron (P++) implantation on top of 320 nm USG layer (a) STD: 60 keV, $5 \times 10^{15} \text{ cm}^{-2}$ (b) 160 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 180 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 190 keV, $5 \times 10^{15} \text{ cm}^{-2}$ and on top of 400 nm USG layer (c) 160 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 180 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 180 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 180 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 190 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 180 keV, $5 \times 10^{15} \text{ cm}^{-2}$ ; 190 keV, $5 \times 10^{15} \text{ cm}^{-2}$ | 100 |

| 4.16 | The figures shows the experiment result of threshold voltage for<br>boron (P++) implantation on top of 320 nm USG layer with various<br>implantations energy (160 keV~180 keV) and STD implantation<br>condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 102 |

| 4.17 | The figures shows the experiment result of on resistance for boron $(P++)$ implantation on top of 320 nm USG layer with various implantations energy (160 keV~180 keV) and STD implantation condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102 |

| 4.18 | The figures shows the experiment result of on resistance for boron $(P++)$ implantation on top of 320 nm USG layer with various implantations energy (160 keV~180 keV) and STD implantation condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 103 |

| 4.19 | The figures shows the experiment result of threshold voltage for boron (P++) implantation on top of 400 nm USG layer with various                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 104 |

implantations energy (160 keV~180 keV) and STD implantation condition

| 4.20 | The figures shows the experiment result of on resistance for boron implantation on top of 400 nm USG layer with various implantations energy (160 keV~180 keV) and STD implantation condition. The box plot for STD group is invisible as the value is far below for comparison with the other two groups | 105 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.21 | The figures shows experiment result of the threshold voltage for various source 1 (arsenic) implantation dosages (3 X $10^{15}$ cm <sup>-2</sup> ~ 6 X $10^{15}$ cm <sup>-2</sup> ) and energy (70 keV~ 120 keV) and STD implantation condition                                                           | 106 |

| 4.22 | The figures shows experiment result of the on resistance for various source 1 (arsenic) dosages (3 X $10^{15}$ cm <sup>-2</sup> ~ 6 X $10^{15}$ cm <sup>-2</sup> ) and energy (70 keV~ 120 keV) and STD implantation condition                                                                            | 107 |

| 4.23 | The figures shows experiment result of the on resistance for various source 1 (arsenic) implantation dosages (3 X $10^{15}$ cm <sup>-2</sup> ~ 6 X $10^{15}$ cm <sup>-2</sup> ) and energy (70 keV~ 120 keV) and STD implantation condition                                                               | 107 |

| 4.24 | The simulation result shows the source 1 (arsenic) profile for the energy 70 keV, $6 \times 10^{15} \text{ cm}^{-2} \& 120 \text{ keV}, 6 \times 10^{15} \text{ cm}^{-2}$                                                                                                                                 | 108 |

| 4.25 | The figures shows experiment result of the threshold voltage for various source 2 (arsenic) implantation dosages $(3.9 \times 10^{15} \text{ cm}^{-2} \sim 7.5 \times 10^{15} \text{ cm}^{-2})$ and STD implantation condition                                                                            | 109 |

| 4.26 | The figures shows experiment result of the on resistance for various source 2 (arsenic) implantation dosages $(3.9 \times 10^{15} \text{ cm}^{-2} \sim 7.5 \times 10^{15} \text{ cm}^{-2})$ and STD implantation condition                                                                                | 109 |

| 4.27 | The figures shows experiment result of the transconduction for various source 2 (arsenic) implantation dosages $(3.9 \times 10^{15} \text{ cm}^{-2} \times 7.5 \times 10^{15} \text{ cm}^{-2})$ and STD implantation condition                                                                            | 110 |

| 4.28 | The figures show diffusion profile of Boron (P++) (a) STD: 900°C,<br>30 minutes + 925 °C ,5 minutes; 900°C, 30 minute (b) 925°C, 15<br>minutes ;925°C,20 minutes                                                                                                                                          | 111 |

| 4.29 | The figures shows threshold voltage for various P++ diffusion condition after P++ implantation into contact hole and STD implantation condition                                                                                                                                                           | 113 |

| 4.30 | The figures shows on resistance for various $P++$ diffusion condition<br>after $P++$ implantation into contact hole and STD implantation<br>condition                                              | 114 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.31 | The figures show simulation results of the diffusion profile of source 1 (arsenic) (a) STD: 900°C, 30 minutes + 900 °C,60 minutes (b) 900°C, 60 minutes                                            | 115 |

| 4.32 | The figure shows the experiment result of the threshold voltage for various source1 implantation, P++ implantations into contact hole, P++ implantation with spacers or STD implantation condition | 117 |

| 4.33 | The figure shows the experiment result of the on resistance for various source 1 implantations, P++ implantation into contact hole, P++ implantation with spacers or STD implantation condition    | 118 |

| 4.34 | The figure shows the experiment result of the transconduction for various source 1 implantations, P++ implantation into contact hole, P++ implantation with spacers or STD implantation condition  | 118 |

| 4.35 | The cross section shows the misaligned contact hole (a) $\pm$ -0.4 um vs (b) STD specification $\pm$ -0.2 um. The contact hole opening is $\sim$ 2.5 um.                                           | 119 |

| 4.36 | The figure shows the experiment result of the threshold voltage for $P++$ implantation with misaligned contact hole overlay (+/-0.4 um), centre overlay (+/-0.2 um) and STD implantation condition | 120 |

| 4.37 | The figure shows the experiment result of the on resistance for P++ implantation with misaligned contact hole overlay (+/-0.4 um), centre overlay (+/-0.2 um) and STD implantation condition       | 121 |

| 4.38 | The figure shows the experiment result of the transconduction for $P$ ++ implantation with misaligned contact hole overlay (+/-0.4 um), centre overlay (+/-0.2 um) and STD implantation condition  | 121 |

| 4.39 | The figure shows the experiment result of the threshold voltage for various P++ implantations into contact hole with and without resist and STD implantation condition                             | 123 |

| 4.40 | The figure shows the experiment result of the on resistance for various P++ implantations into contact hole with and without resist and STD implantation condition                                 | 123 |

| 4.41 | The figure shows the experiment result of the transconductance for various P++ implantations into contact hole with and without resist and STD implantation condition                                                           | 124 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.42 | Figure shows the SEM cross section of the contact hole structure after contact hole etch                                                                                                                                        | 124 |

| 4.43 | The figure shows the experiment result of the sheet resistance P++ (contact) for P++ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition                    | 126 |

| 4.44 | The figure shows the experiment result of the sheet resistance $P++/P-$ (contact/body) for $P++$ implantation (5 X 10 <sup>15</sup> cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition | 126 |

| 4.45 | The figure shows the experiment result of the contact resistance $M1/P++$ (metal/contact) for P++ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition ion   | 127 |

| 4.46 | The figure shows the experiment result of the sheet resistance $N+/P++$ (source/ contact) for P++ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition       | 127 |

| 4.47 | The figure shows the experiment result of the sheet resistance S1 (polysilicon) for P++ implantation $(5 \times 10^{15} \text{ cm}^{-2})$ into contact hole with and without resist and STD implantation condition              | 128 |

| 4.48 | The figure shows the experiment result of the contact resistance M1/S1 (metal/polysilicon) for P++ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition      | 128 |

| 4.49 | The figure s shows the experiment result of the threshold voltage for $P++$ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition                             | 130 |

| 4.50 | The figure shows the experiment result of the on resistance for P++ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition                                     | 130 |

| 4.51 | The figure shows the experiment result of the transconduction for $P++$ implantation (5 X $10^{15}$ cm <sup>-2</sup> ) into contact hole with and without resist and STD implantation condition                                 | 131 |

## LIST OF APPENDICES

| Appendix |                                                                                                                     | Page |

|----------|---------------------------------------------------------------------------------------------------------------------|------|

| 1.1      | Table shows the ratings of power semiconductor devices                                                              | 147  |

| 4.1      | Figure shows input capacitance, Ciss Characteristics for spacer free (ENG) and reference (REF) samples              | 148  |

| 4.2      | Figure shows output capacitance, Coss characteristics for spacer free (ENG) and reference (REF) samples             | 149  |

| 4.3      | Figure shows reverse transfer capacitance, Crss characteristics for spacer free (ENG) and reference (REF) samples   | 150  |

| 4.4      | Figure shows transfer characteristics for spacer free sample (Ratio) and reference (REF) samples                    | 151  |

| 4.5      | Figures show output characteristic for (a) reference (b) spacer free                                                | 152  |

| 4.6      | Figure shows turn-on switching: $R_g$ =14.70hm, $I_D$ =20.7A, $V_{gs}$ =15V                                         | 153  |

| 4.7      | Figure shows turn-off switching: $R_g$ =14.70hm, $I_D$ =20.7A, $V_{gs}$ =15V                                        | 154  |

| 4.8      | Figure shows gate charge for spacer free (Ratio) and reference samples                                              | 155  |

| 4.9      | Figure shows avalanche characterization (avalanche single pulse energy) for spacer free (Ratio) and reference group | 156  |

| 4.10     | Figure shows short circuit destruction for spacer free (Ratio) and reference group                                  | 157  |

| 4.11     | Figure shows body diode reverse recovery charge for spacer free (Ratio) and reference group                         | 158  |

| 5.1      | Table shows the process flow of Standard , Concept 1, Concept 2 , Concept 3 (a) and Concept 3 (b) Groups            | 159  |

| 5.2      | Table shows the cycle time for Standard , Concept 1, Concept 2, Concept 3 (a) and Concept 3 (b) Groups              | 160  |

# LIST OF SYMBOLS & ABBREVIATIONS

| BJT             | Bipolar junction transistor                                    |

|-----------------|----------------------------------------------------------------|

| BPSG            | Borophosphosilicate Glass                                      |

| BSG             | Boro-silicate glass                                            |

| Cds             | Drain-to-source capacitance                                    |

| C <sub>GD</sub> | Gate-to-drain capacitance                                      |

| CGS             | Gate-to-source capacitance                                     |

| Ciss            | Input capacitance                                              |

| Coss            | Output capacitance                                             |

| Crss            | Reverse transfer capacitance                                   |

| CoolMOS         | Cool- Metal-oxide-semiconductor field-effect transistor        |

| CVD             | Chemical Vapour Depostion                                      |

| D-MOSFET        | Depletion -Metal-oxide-semiconductor field-effect transistor   |

| DOE             | Design of experiment                                           |

| E-MOSFET        | Enhancement- Metal-oxide-semiconductor field-effect transistor |

| FT              | Functional Test                                                |

| GTO             | Gate-turn-off thyristors                                       |

| HCI             | Hydrochloride acid                                             |

| HDPCVD          | High-density plasma chemical vapor deposition                  |

| HF              | Hydroflouric acid                                              |

| $H_2$           | Hydogen flow                                                   |

| IGBT            | Insulated gate bipolar transistor                              |

| LPCVD           | Low Pressure Chemical Vapour Deposition                        |

| LTO             | Low temperature oxide                                          |

| MOS                                                     | Metal-oxide-semiconductor                                                                       |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| MOSFET                                                  | Metal-oxide-semiconductor field-effect transistor                                               |  |  |

| O <sub>2</sub>                                          | Oxygen                                                                                          |  |  |

| P++                                                     | Contact (Boron)                                                                                 |  |  |

| PCM                                                     | Process Control Monitoring                                                                      |  |  |

| POSA MOS                                                | Polysilicon oxidation self-aligned MOS                                                          |  |  |

| POC1 <sub>3</sub>                                       | Phosphorus oxygen chloride                                                                      |  |  |

| PSG                                                     | Phosphosilitcate Glass                                                                          |  |  |

| Qds                                                     | Drain-to-source charge                                                                          |  |  |

| $Q_{GD}$                                                | Gate-to-drain charge                                                                            |  |  |

| Q <sub>GS</sub>                                         | Gate-to-source charge                                                                           |  |  |

| Ra                                                      | Accumulation resistance                                                                         |  |  |

| R <sub>B</sub>                                          | Base Resistance                                                                                 |  |  |

| RCT                                                     | Reverse-conducting thyristors                                                                   |  |  |

| Rc (M1/N+/P++) Contact resistance- metal/source/contact |                                                                                                 |  |  |

| Rc (M1/P++)                                             | Contact resistance -metal/contact                                                               |  |  |

| Rc (M1/S1)                                              | Contact resistance-metal/ polysilicon                                                           |  |  |

| Rch                                                     | Channel resistance                                                                              |  |  |

| RDS(On)                                                 | Drain to source resistance (on)                                                                 |  |  |

| Repi                                                    | "JFET" component-resistance of the region between the two body regions, drift region resistance |  |  |

| Rn                                                      | Source diffusion resistance                                                                     |  |  |

| Rs                                                      | Source contact resistance                                                                       |  |  |

| Rs (N+/P++)                                             | Sheet resistance- source/contact                                                                |  |  |

| Rs (S1)                                                 | Sheet resistance-polysilicon                                                                    |  |  |

| Rs (P++/P-)                                             | Sheet resistance-contact /body                                                                  |  |  |

| Rs (P++)          | Sheet resistance- contact                                                                                                                                                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rsub              | Substrate resistance                                                                                                                                                                                                                                                        |

| Rwcml             | Sum of bond wire resistance, the contact resistance between the<br>source and drain metallization and the silicon, metallization and<br>leadframe contributions. These are normally negligible in high<br>voltage devices but can become significant in low voltage devices |

| RTA               | Rapid thermal annealing                                                                                                                                                                                                                                                     |

| R <sub>TH</sub>   | Thermal impedance                                                                                                                                                                                                                                                           |

| SiO <sub>2</sub>  | Silicon dioxide                                                                                                                                                                                                                                                             |

| SOI               | Silicon-on-insulator                                                                                                                                                                                                                                                        |

| SJ                | Super junction                                                                                                                                                                                                                                                              |

| TEOS              | Tetraethylorthosilicate                                                                                                                                                                                                                                                     |

| TiSi <sub>2</sub> | Titanium disilicide                                                                                                                                                                                                                                                         |

| USG               | Undoped Silicate Glass                                                                                                                                                                                                                                                      |

| UPS               | Uninterruptible power supplies                                                                                                                                                                                                                                              |

| $V_{BE}$          | Base to emitter voltage                                                                                                                                                                                                                                                     |

| Vds               | Drain-to-source voltage                                                                                                                                                                                                                                                     |

| VGS               | Gate to source voltage                                                                                                                                                                                                                                                      |

| $V_{TH}$          | Threshold voltage                                                                                                                                                                                                                                                           |

| SEM               | Scanning Electron Microscope                                                                                                                                                                                                                                                |

| STD               | Standard                                                                                                                                                                                                                                                                    |

|                   |                                                                                                                                                                                                                                                                             |

#### PEMBANGUNAN KONSEP MENJAJARKAN PENIMPALAN KONTAK BAGI TRANSISTOR KUASA TINGGI

#### ABSTRAK

Mengoptimasi skema proses integrasi bagi sesebuah teknolgi merupakan salah satu faktor penting untuk mengurangkan bilangan kecatatan dan kitaran masa dalam bidang fabrikasi wafer. Dalam pengajian sarjana ini, aliran proses yang dioptimasi bagi menjajarkan penimpalan kontak telah dikaji bagi teknologi Infineoen CoolMOS. Selepas mengaji 3 idea yang berlainan dengan insentif, konsep yang paling berpotensi tinggi dipilih bagi pengoptimasian dan pencirian lanjutan di peringkat wafer dan poduk. Teknologi pada masa kini menggunakan dinding-tepi penjarakan, di mana ia dibentuk melalui taburan silikon dioksida dan diikuti oleh pengoressan oxida bukan isotropik bagi membentuk lubang penimpalan kontak. Dalam konsep pertama dan kedua, oksida polisilikon dan kaca silikate tanpa dop (USG) masing-masing digunakan untuk menggantikan penjarakkan and menjalankan penimpalan kontak. Penghadan peralatan fabrikasi dan pengaruh terhadap percirian wafer menyebabakan konsep-konsep ini tidak dapat dilaksanakan sepenuhnya dalam pengeluaran. Konsep ketiga menjalankan skema pengintegrasian tanpa penjarakkan dinding tepi. Penimpalan kontak dijalankan selepas proses pengoressan kontak lubang polisilikon. Dengan mengaplikasikan konsep ini, sebilangan langkah proses boleh disingkirkan. serta bilangan kecatatan dalam wafer dan kitaran masa untuk menfabrikasikan sesuatu transistor boleh dikurangkan. Pencirian insentif peringkat wafer dan produk mendedahkan 1:1 yang cirinya bersesuian dengan pretasi produk konsep asal serta pertimbangan khas telah diberikan bagi menganalisakan parameter transistor seperti rintangan keadaan aktif, voltan permulaan dan pengaliran arus. Kesemua keputusan telah dibentangkan and dibincangkan dengan teliti bagi memaparkan potensi baik konsep baru ini.

xix

#### DEVELOPMENT OF SPACER FREE SELF-ALIGNED CONTACT IMPLANTATION FOR POWER DEVICES

#### ABSTRACT

Optimization of the process integration scheme for a technology is one of the key factors within wafer fabrication in order to reduce defect density and production cycle time. Within this master study, an optimized process flow for the self-aligned contact implantation was evaluated for the Infineons CoolMOS technology. After intensive feasibility investigations of 3 different ideas, the most promising concept was further optimized and characterized on wafer level as well as in the final product. The current technology utilizes side-wall spacers, which are formed by deposition of silicon dioxide followed by an anisotropic oxide etched prior to contact-hole implantation. Within the first and second concept, the original spacer process block spacer was replaced with an alternative spacer fabricated by oxidation of the gate polysilicon and deposition of undoped silicate glass (USG), respectively. Limitations of certain fabrication tools as well as influences on the device characteristics did not allow these concepts to be executed in the production. The third and the most promising concept facilitates contact implantation after the polysilicon contact hole-etch process. By applying this concept, a number of process steps can be removed, which as a consequence greatly reduces the frontend defect density of the wafer as well as cycle time to fabricate the transistor. Intensive characterization of wafer and dies revealed a 1:1 match to the current product performance and special consideration has been given on the analysis of the 'on resistance', 'threshold voltage' transistor parameters, such as and 'transconductance'. The results are presented and discussed clearly showing the potential of the new concept.

XX

#### **CHAPTER 1**

#### INTRODUCTION

#### **1.1 Project Introduction**

Semiconductor power devices are electronic components used as rectifiers or switches in electronic circuits. A majority of these devices are made of silicon however other materials, such as silicon carbide is under development. With the development of power semiconductor technology, the power handling capabilities and the switching speed of the power devices have improved tremendously (Spulber *et al.*, 1999).

Semiconductor power devices can be divided widely into three types; which are diodes, transistors and thyristors. A diode is a two-terminal pn-junction device and it serves three purposes: (1) general purpose diodes, (2) high speed (or fast recovery) diodes and (3) Schottky diodes. General purpose diodes are used in low-speed applications whereas fast-recovery diodes are essential for high-frequency switching. Schottky diodes have low on-state voltage and very small recovery time (Muhammad, 2004).

A thyristor has three terminals, which are an anode, a cathode and a gate. The thyristors can be divided into many types, such as line-commutated thyristors, gate-turn-off thyristors (GTO), reverse-conducting thyristors (RCT) and others. Conventional thyristors are designed without gate-controlled turn-off capability, in which the conducting state of the thyristor can be recovered from its nonconducting

1

state when the current is brought to zero by other means. GTOs are designed to have both controlled turn-on and -off capability. Thyristors have lower on-state conduction losses and higher power handling capability compared to transistors.

On the other hand, transistors generally have superior switching performances in terms of faster switching speed and lower switching losses. Some common power transistors are metal-oxide-semiconductor field-effect transistor (MOSFET), bipolar junction transistor (BJT) and insulated gate bipolar transistor (IGBT). Generally, transistors are built using a vertical structure; whereas lateral structure is used for small-signal applications. BJT is a current-controlled device, in which amount of collector current is controlled by base current. An IGBT is inherently faster than BJT. However, the switching speed of IGBTs is inferior to that of MOSFETs (Appendix 1.1).

The two basic types of MOSFET are depletion (D) and enhancement (E) MOSFET. The D-MOSFET operates in the depletion or enhancement mode whereas the E-MOSFET only operates in the enhancement mode and has no depletion mode. N-channel MOSFET operates in depletion mode when a negative gate-to-source voltage is applied and when a positive gate-to-source voltage is applied, an enhancement mode is obtained. For an n-channel MOSFET, the channel is induced by the application of a gate to source voltage, VGS greater than the threshold value,  $V_{TH}$ . Power transistors are designed to achieve higher current, voltage and power capability by creating shorter channel between drain and source.

In this project, COOLMOS 600V have been used in the evaluations. CoolMOS virtually combines the low switching losses of a MOSFET with the low on-state losses of an IGBT (Figure 1.1) (Muhammad, 2004). In comparison with classical MOS

2

structure, CooLMOS, incorporates two additional p- columnar layers sandwiched between n-type drift regions. The on-resistance could be reduced by a factor of 5 in comparison to the classical device due to the super-junction formation. This is achieved by controlling the charge between the p- and n-type layers in such a way that the n-type doping concentration is increased beyond the upper limit set by the breakdown voltage considerations of a conventional power MOSFET (Lorenz *et al.*, 1999).

Figure 1.1: Cross section of conventional (a) Field-stop IGBT, (b) D-MOSFET and (c) CoolMOS (Deboy *et al.*, 1998).

A sufficient contact between source and drain is crucial for the functioning of these devices. A widely used concept to achieve this is to align the contact implantation on the polysilicon gate and source region through a spacer formed by Tetraethylorthosilicate (TEOS)-based silicon dioxide and followed by an anisotropic etch of the oxide. For n-type transistors this contact implantation is also referred to P++ implantation.

The advantage of having a spacer is to avoid an additional photolayer which is required to align the contact implantation away from the channel region. Additionally, the spacer is able to effectively isolate the contact implantation from the channel area (Figure 1.2) and that is why the concept is also referred to self-aligned contact implantation. This means that they prevent dopants from diffusing under the gate during the implantation of the highly doped source regions and affects the device performance. The shallow diffused P++ surface below the source region helps to reduce the P-base sheet resistance and its contact resistance (Shenai,1992)<sup>a</sup>. With the spacer concept, the base length ( $R_{base}$ ) of the transistor inherent parasitic bipolar structure can be minimized to the outer most extent. Thus, no latch-up phenomenon within the specified safe operating area of the transistor will be occurred (Deboy *et al.*, 1998).

Figure 1.2: Cross section of power transistor device (Trobin W, 2005)

#### **1.2 Problem Statement**

Structure of power devices are often modified to make them operate at higher current density and lower on resistance. In this thesis, electrical and dynamic results of power transistors fabricated without using sidewall spacers have been reported. Side wall spacers are formed by TEOS based silicon dioxide and followed by anisotropic etch of the oxide. The advantage of this concept without spacer is that no additional photolayer for the alignment is needed. However, relatively thick spacer oxide, which is formed by TEOS based oxide deposition may increase defect density of the product and rather extensive maintenance of the tool is required.

In the past, DMOSFET cells with shallow p+ diffusion have been demonstrated using a polysilicon mask (Nakagawa *et al.*, 1986) and Phosphosilitcate Glass (PSG) spacers (Mori *et al.*, 1988) to block boron implant. However, these approaches lead to degradation of cell packing density, complex processing, and poor wafer yield. To reduce the gate resistance and to improve the source contact resistance, refractory metal/silicide technologies have been used (Shenai *et al.* 1989 <sup>a</sup> ,Shenai *et al.* 1989 <sup>b</sup> ,Shenai *et al.* 1989 <sup>c</sup>). Spacers are made by dry etching, which happens much faster in the vertical direction (depth) than in the lateral directions. Since the TEOS-based silicon dioxide layer is thicker next to the gate electrodes, it will take much longer time to etch it. If the etching is stopped once the silicon wafer is reached, TEOS-based silicon dioxide will still be left next to the gate electrodes. These are the oxide spacers.

The built of spacers involves many processes, such as TEOS-based silicon dioxide deposition, anisotropic etch of TEOS-based silicon dioxide, furnace anneal and various cleaning steps. These processes eventually increase the possibility of defect density during the production run. Besides, the quality of the deposited oxide is not that good; a densification is required. Starting with the 250 nm technology node, the oxide spacers become unsuitable for three reasons, which are field oxide loss, high thermal budget and oxide spacers are vulnerable. The part of the field oxides is also lost during