# A 0.13-μm CMOS RECONFIGURABLE POWER CONSTRAINED SIMULTANEOUS NOISE AND INPUT MATCHING (PCSNIM) LOW NOISE AMPLIFIER (LNA) FOR MULTI-STANDARD 0.9, 1.8 AND 2.1 GHz MOBILE APPLICATION

# **AWATIF BINTI HASHIM**

UNIVERSITI SAINS MALAYSIA 2016

# A 0.13-μm CMOS RECONFIGURABLE POWER CONSTRAINED SIMULTANEOUS NOISE AND INPUT MATCHING (PCSNIM) LOW NOISE AMPLIFIER (LNA) FOR MULTI-STANDARD 0.9, 1.8 AND 2.1 GHz MOBILE APPLICATION

by

#### **AWATIF BINTI HASHIM**

Thesis submitted in fulfillment of the requirements for the degree of Master of Science

**June 2016**

## **DECLARATION**

I hereby declare that the work in this thesis is my own except for quotations and summaries which have been duly acknowledged.

8th June 2016 Awatif Binti Hashim

P-LM0442

#### ACKNOWLEDGEMENT

In the name of Allah, Most Gracious, Most Merciful.

My deepest gratitude to my first supervisor, Assoc. Prof. Dr. Norlaili Mohd Noh and my second supervisor, Dr. Mohd Tafir bin Mustaffa for their patience and guidance throughout this project. Their generosity for guiding me and sharing their expert knowledge is very much appreciated.

I would also like to acknowledge Silterra (M) Sdn Bhd for providing the model libraries and CEDEC as an excellence Design Centre that provides high capability of software and equipments. I am thankful to all CEDEC staffs for helping me especially with the usage of the design tool. Their prompt feedback on any tool referred problem is highly appreciated.

Special thanks to my husband, parents and family who provides me with their endless support. My gratitude to them is beyond what I can express in words. Last but not least, thanks to everyone who have contributed directly or indirectly to the success of this project and the completion of this thesis.

# TABLE OF CONTENTS

|         |                                                          | Page  |

|---------|----------------------------------------------------------|-------|

| Ackno   | owledgement                                              | ii    |

| Table   | of Contents                                              | iii   |

| List of | f Tables                                                 | . vi  |

| List of | f Figures                                                | vii   |

| List of | f Abbreviations                                          | X     |

| List of | f Symbols                                                | xii   |

| Abstra  | ak                                                       | xvi   |

| Abstra  | act                                                      | xviii |

|         |                                                          |       |

| CHAF    | PTER 1 - INTRODUCTION                                    |       |

| 1.1     | Introduction                                             | 1     |

| 1.2     | Motivation                                               | 3     |

| 1.3     | Objectives                                               | 5     |

| 1.4     | Scope                                                    | 6     |

| 1.5     | Thesis Outline                                           | 6     |

|         |                                                          |       |

| СНАР    | PTER 2 - THEORETICAL BACKGROUND AND LITERATURE           |       |

| REVI    | EW                                                       |       |

| 2.1     | Mobile application                                       | 8     |

| 2.2     | Low Noise Amplifier                                      | 9     |

|         | 2.2.1 Power constrained and simultaneous noise and input |       |

|         | matching circuit (PCSNIM) topology                       | 10    |

|         | 2.2.1 (a) Inductively degenerated circuit                | 10    |

|         | 2.2.1 (b) The cascode circuit                            | 11    |

|      | 2.2.1 (c)  | Simultaneous Noise and Input Matching (SNIM) LNA        | 11 |  |

|------|------------|---------------------------------------------------------|----|--|

|      | 2.2.1 (d)  | Power-constrained Simultaneous Noise and Input Matching |    |  |

|      |            | (PCSNIM) LNA                                            | 15 |  |

| 2.3  | MOS swi    | tch                                                     | 18 |  |

| 2.4  | Low Nois   | se Amplifier                                            | 22 |  |

|      | 2.4.1 S    | cattering parameters                                    | 22 |  |

|      | 2.4.2 G    | ain                                                     | 24 |  |

|      | 2.4.3 N    | loise figure                                            | 24 |  |

|      | 2.4.4 L    | inearity measures                                       | 25 |  |

| 2.3  | Similar w  | ork by others                                           | 27 |  |

|      |            |                                                         |    |  |

| СНАІ | PTER 3 - M | IULTI-STANDARD LNA DESIGN AND LAYOUT                    |    |  |

| CONS | SIDERATIO  | ON                                                      |    |  |

| 3.1  | Specificat | tion                                                    | 34 |  |

| 3.2  | Flowchar   | t of the project implementation                         | 35 |  |

| 3.3  | Multi-star | ndard LNA using CMOS switches                           | 37 |  |

| 3.4  | Multi-star | ndard LNA design flow                                   | 42 |  |

|      | 3.4.1 C    | Component values                                        | 44 |  |

| 3.5  | Layout pr  | reparation                                              | 46 |  |

| 3.6  | Layout co  | onsideration                                            | 46 |  |

|      | 3.6.1 P    | reparation of layout                                    | 47 |  |

|      | 3.6.2 P    | arasitics                                               | 48 |  |

| 3.7  | General la | ayout techniques                                        | 50 |  |

| 3.8  | Measuren   | Measurement setup                                       |    |  |

| 3.9  | The micro  | ograph of multi-standard LNA                            | 51 |  |

## CHAPTER 4 – DESIGN IMPLEMENTATION

| 4.1  | Pre-lay | yout simulation results                                    | 54 |

|------|---------|------------------------------------------------------------|----|

| 4.2  | Post-la | yout simulation results                                    | 59 |

| 4.3  | Measu   | rement results                                             | 63 |

|      | 4.3.1   | S-parameter performance.                                   | 63 |

|      | 4.3.2   | NF performance                                             | 65 |

|      | 4.3.3   | Linearity performance                                      | 66 |

| 4.8  | Summ    | ary and the comparison of pre-, post-layout simulation and |    |

|      | measu   | rement results                                             | 69 |

|      |         |                                                            |    |

| CHAI | PTER 5  | – CONCLUSION AND FUTURE WORKS                              |    |

| 5.1  | Conclu  | usions                                                     | 73 |

| 5.2  | Future  | work                                                       | 75 |

|      |         |                                                            |    |

| REFE | RENCE   | S                                                          | 77 |

| APPE | NDICE   | S                                                          |    |

| LIST | OF PUB  | BLICATIONS                                                 |    |

# LIST OF TABLES

|           |                                                      | Page |

|-----------|------------------------------------------------------|------|

| Table 2.1 | Wireless standards (Tasic, 2007)                     | 9    |

| Table 2.2 | LNA performance metrics from similar work by others  | 33   |

| Table 3.1 | LNA specification                                    | 36   |

| Table 3.2 | C <sub>tot</sub> at different frequency              | 39   |

| Table 3.3 | Switches Condition                                   | 40   |

| Table 3.4 | Component values                                     | 45   |

| Table 4.1 | Optimized layout                                     | 60   |

| Table 4.2 | Pre-, post-layout simulation and measurement results | 71   |

## LIST OF FIGURES

|                       | P                                                                                                                                                                                           | age      |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

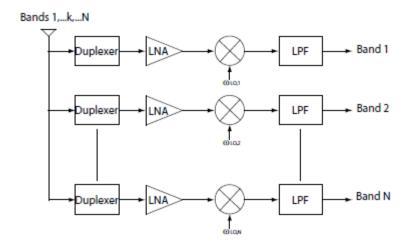

| Figure 1.1            | Block diagram of a multi-band receiver using parallel                                                                                                                                       |          |

|                       | architecture. (El-Nozahi, 2010)                                                                                                                                                             | 2        |

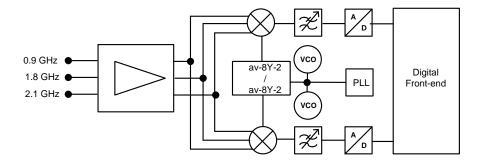

| Figure 1.2            | Block diagram of a multi-standard receiver with single LNA (Gustafsson, 2006)                                                                                                               | 2        |

| Figure 2.1            | Example of an inductively degenerated transistor                                                                                                                                            | 11       |

| Figure 2.2            | Example of a cascode circuit                                                                                                                                                                | 12       |

| Figure 2.3            | The SNIM cascode LNA                                                                                                                                                                        | 12       |

| Figure 2.4            | The small-signal model with noise sources of the SNIM cascode                                                                                                                               | 14       |

| Figure 2.5            | The PCSNIM LNA (Noh, 2009)                                                                                                                                                                  | 16       |

| Figure 2.6            | $I_D$ vs $V_D$                                                                                                                                                                              | 18       |

| Figure 2.7            | (a) Schematic symbol of a switch; (b) NMOS as a switch; (c) equivalent circuit of MOS as switch when turned on; (d) equivalent circuit of MOS as switch when turned off (Huang et al. 2007) | 19       |

| Figure 2.8 Figure 2.9 | <ul><li>(a) The switching capacitor;</li><li>(b) when Msw is turned off;</li><li>(c) when Msw is turned on (Hung, 2010)</li><li>Important features in LNA</li></ul>                         | 20<br>22 |

| Figure 2.10           | Two-port network (Said, 2011)                                                                                                                                                               | 23       |

| Figure 2.11           | 1-dB compression point (Lee, 2004)                                                                                                                                                          | 26       |

| Figure 2.12           | Third order intercept point (Lee, 2004)                                                                                                                                                     | 27       |

| Figure 2.13           | Schematic of the LNA design by Mustaffa (Mustaffa, 2009)                                                                                                                                    | 28       |

| Figure 2.14           | Schematic of the LNA design by Liscidini (Liscidini, 2006).                                                                                                                                 | 29       |

| Figure 2.15           | Schematic of the LNA design by Balemarthy (Balemarthy, 2008)                                                                                                                                | 30       |

| Figure 2.16           | Schematic of the LNA design by Khoo (Khoo, 2011)                                                                                                                                            | 31       |

| Figure 2.17           | Schematic of the LNA design by Aravint (Aravint, 2015)                                                                                                                                      | 32       |

| Figure 2.18           | Schematic of the LNA design by Wang (Wang, 2010)                                                                                                                                            | 32       |

| Figure 3.1  | Flowchart of the project implementation                                   | 36 |

|-------------|---------------------------------------------------------------------------|----|

| Figure 3.2  | Multi-standard LNA design                                                 | 38 |

| Figure 3.3  | Small signal of the input multi-standard LNA                              | 38 |

| Figure 3.4  | Flow chart of the multi-standard LNA design                               | 43 |

| Figure 3.5  | Layout of multi-standard LNA                                              | 47 |

| Figure 3.6  | Capacitance in an IC                                                      | 49 |

| Figure 3.7  | S-parameter measurement setup of the input and output stages (Mohd, 2010) | 51 |

| Figure 3.8  | The measurement setup                                                     | 52 |

| Figure 3.9  | The micrograph of multi-standard LNA                                      | 52 |

| Figure 4.1  | Pre-layout input return losses of multi-standard LNA design               | 54 |

| Figure 4.2  | Pre-layout output return losses of multi-standard LNA design              | 55 |

| Figure 4.3  | Pre-layout power gain of multi-standard LNA design                        | 55 |

| Figure 4.4  | Pre-layout reverse isolation of multi-standard LNA design                 | 56 |

| Figure 4.5  | Simulated NF of multi-standard LNA design                                 | 56 |

| Figure 4.6  | Simulated IP <sub>1dB</sub> at 0.9 GHz                                    | 57 |

| Figure 4.7  | Simulated IP <sub>1dB</sub> at 1.8 GHz                                    | 58 |

| Figure 4.8  | Simulated IP <sub>1dB</sub> at 2.1 GHz                                    | 58 |

| Figure 4.9  | Simulated IIP <sub>3</sub> at 0.9 GHz                                     | 58 |

| Figure 4.10 | Simulated IIP <sub>3</sub> at 1.8 GHz                                     | 59 |

| Figure 4.11 | Simulated IIP <sub>3</sub> at 2.1 GHz                                     | 59 |

| Figure 4.12 | Post-layout input return losses of multi-standard LNA design              | 60 |

| Figure 4.13 | Post-layout output return losses of multi-standard LNA design             | 61 |

| Figure 4.14 | Post-layout power gain of multi-standard LNA design                       | 61 |

| Figure 4.15 | Post-layout reverse isolation of multi-standard LNA design                | 62 |

| Figure 4.16 | Post-layout NF of multi-standard LNA design                               | 62 |

| Figure 4.17 | Measured input return losses of multi-standard LNA design  | 63 |

|-------------|------------------------------------------------------------|----|

| Figure 4.18 | Measured output return losses of multi-standard LNA design | 64 |

| Figure 4.19 | Measured power gain of multi-standard LNA design           | 64 |

| Figure 4.20 | Measured reverse isolation of multi-standard LNA design    | 65 |

| Figure 4.21 | Measured NF of multi-standard LNA design                   | 66 |

| Figure 4.22 | Measured IP <sub>1dB</sub> at 0.9 GHz                      | 66 |

| Figure 4.23 | Measured IP <sub>1dB</sub> at 1.8 GHz                      | 67 |

| Figure 4.24 | Measured IP <sub>1dB</sub> at 2.1 GHz                      | 67 |

| Figure 4.25 | Measured IP <sub>3</sub> at 0.9 GHz                        | 68 |

| Figure 4.26 | Measured IP <sub>3</sub> at 1.8 GHz                        | 68 |

| Figure 4.27 | Measured IP <sub>3</sub> at 2.1 GHz                        | 69 |

#### LIST OF ABBREVIATIONS

2G Second-generation wireless telephone technology

3G Third generation of mobile telecommunications technology

CEDEC Collaborative Microelectronic Design Excellence Centre

CMOS Complementary metal oxide semiconductor

CR Current Reuse

C Correlation coefficient

CC Coupling capacitor

dB Decibel

DCS Digital Cellular System

DUT Device Under Test

DRC Design Rule Check

F Noise Factor

FC Folded Cascode

GPS Global Positioning System

G-S Gate-Source

GSM Global System for Mobile

I Current

IC Integrated Circuits

IDCS Inductively-degenerated common source

IP<sub>1dB</sub> Input 1-dB Compression Point

IIP<sub>3</sub> Input-Referred Third-Order Intermodulation Point

IM Inter-Modulation

ISS Impedance Standard Substrate

LNA Low Noise Amplifier

MOS Metal Oxide Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect-Transistor

NF Noise Figure

NF<sub>min</sub> Minimum Noise Figure

NMOS N-Metal Oxide Semiconductor

OP<sub>1dB</sub> Output 1-dB Compression Point

OIP<sub>3</sub> Output-Referred Third-Order Intermodulation Point

P<sub>1dB</sub> 1-dB Compression Point

P<sub>in</sub> Input Power

PCSNIM Power-Constrained Simultaneously Noise and Input Matching

PMOS P-Metal Oxide Semiconductor

P<sub>out</sub> Output Power

R Resistance

R<sub>on</sub> Output resistance of the MOSFET

RF Radio Frequency

USM Universiti Sains Malaysia

V Voltage

W width of MOSFET

W-CDMA Wideband Code Division Multiple Access

WLAN Wireless Local Area Networks

#### LIST OF SYMBOLS

$\alpha$  alpha

$\delta$  delta

$\gamma$  gamma

$\Omega$  Ohm

$\chi \hspace{1cm} Chi$

μ micron

r Resistivity

log Logarithm

G Transducer gain

C<sub>c</sub> Coupling capacitor

C<sub>eq</sub> Equivalent capacitance

C<sub>1</sub> Capacitor 1

C<sub>2</sub> Capacitor 2

c<sub>gs</sub> Gate-source capacitance

c<sub>gd</sub> Gate-drain capacitance

C<sub>d1</sub> Drain capacitor 1

C<sub>ex1</sub> External capacitor 1 at the input

C<sub>ex2</sub> External capacitor 2 at the input

C<sub>ex3</sub> External capacitor 3 at the input

C<sub>Msw3</sub> Switch 3 capacitance

C<sub>Msw4</sub> Switch 4 capacitance

C<sub>o</sub> Output capacitor

C<sub>ox</sub> Oxide capacitor

C<sub>t</sub> Total capacitance

C<sub>tot</sub> Total capacitance

f Frequency (Hz)

F Noise factor

G Transducer gain

G<sub>a</sub> Available gain

g<sub>m</sub> Transconductance

I Current (A)

I<sub>DC</sub> Current flow through a device

I<sub>h</sub> Current handling constant

L Length of the transistor/material

L<sub>d1</sub> Drain inductor 1

L<sub>d2</sub> Drain inductor 2

L<sub>s</sub> Source inductor

L<sub>g</sub> Gate inductor

M<sub>1</sub> Transistor 1

M<sub>2</sub> Transistor 2

M<sub>SW1</sub> Transistor switch 1

M<sub>SW2</sub> Transistor switch 2

M<sub>SW3</sub> Transistor switch 3

M<sub>SW4</sub> Transistor switch 4

N<sub>a</sub> Noise added by the amplifier

N<sub>i</sub> Noise power levels at the input to the amplifier

Noise power levels at the output to the amplifier

P Power

Q<sub>s</sub> Quality factor

Q<sub>s,opt</sub> Optimum quality factor

R Resistance

R<sub>1</sub> Resistor 1

R<sub>s</sub> Sheet resistance

S<sub>11</sub> Input reflection coefficient

S<sub>21</sub> Forward transmission coefficient

S<sub>12</sub> Reverse transmission coefficient

S<sub>22</sub> Output reflection coefficient

Signal at the input to the amplifier

S<sub>o</sub> Signal at the output to the amplifier

T Thickness of the material

V<sub>BIAS\_1</sub> Bias volatage 1

V<sub>BIAS 2</sub> Bias volatage 2

V<sub>DS</sub> Drain-Source voltage

V<sub>GS</sub> Gate-Source voltage

V<sub>in</sub> Input voltage

V<sub>ov</sub> Overdrive voltage

V<sub>th</sub> Threshold voltage

W Width of transistor

W<sub>M1</sub> Width of transistor 1

W<sub>M2</sub> Width of transistor 2

W<sub>MSW1</sub> Width of transistor switch 1

W<sub>MSW2</sub> Width of transistor switch 2

W<sub>MSW3</sub> Width of transistor switch 3

W<sub>MSW4</sub> Width of transistor switch 4

$\omega_{o}$  Omega

$\omega_T$  Transition frequency

Z<sub>in</sub> Input impedance

Z<sub>Msw</sub> Impedance switch

$Z_{Msw1}$  Impedance of switch 1

$Z_{Msw2}$  Impedance of switch 2

$Z_{Msw3}$  Impedance of switch 3

$Z_{Msw4}$  Impedance of switch 4

Z<sub>opt</sub> Input noise

# SATU 0.13-µm CMOS PADANAN MASUKAN DAN HINGAR SERENTAK DENGAN KEKANGAN KUASA PENGUAT HINGAR RENDAH BOLEH KONFIGURASI SEMULA BAGI APLIKASI MUDAH ALIH BERBILANG PIAWAIAN 0.9, 1.8 DAN 2.1 GHz

#### **ABSTRAK**

Industri komunikasi tanpa wayar sedang mengalami pertumbuhan yang luar biasa. Sebelum ini, penerima berbilang piawaian telah direka dalam seni bina yang selari untuk menampung berbilang piawai. Walaubagaimanapun, untuk setiap laluan, kawasan bentangan yang besar membuatkan kos fabrikasi meningkat. Sebagai tindakbalas terhadap permintaan untuk bahagian hadapan tanpa wayar yang berkos rendah dan berprestasi lebih tinggi, banyak kajian intensif pada CMOS frekuensi radio (RF ) litar bahagian hadapan telah dijalankan. Projek ini menggabungkan laluan-laluan selari tersebut kepada kaedah penerima tanpa wayar laluan tunggal. Matlamat utama adalah untuk meminimumkan "trade-off" atau mencapai keseimbangan antara prestasi tinggi, saiz yang lebih kecil dan kos rendah pada reka bentuk penggunaan kuasa yang rendah. Sasaran projek ini adalah untuk mereka bentuk penguat hingar rendah (LNA) berbilang piawaian bagi tiga piawai operasi jalur frekuensi. Bagi mendemonstrasi keberkesanan teknik, satu reka bentuk LNA laluan tunggal berbilang piawaian menggunakan konsep pensuisan telah dilaksanakan. Reka bentuk boleh memilih jalur frekuensi operasi dengan mengalihkan suis yang digunakan di rangkaian padanan masukan dan keluaran. Satu LNA berbilang piawaian dengan topologi Padanan Masukan dan Hingar Serentak dengan Kekangan Kuasa (PCSNIM) telah dilaksanakan bagi tujuan ini. LNA beroperasi pada frekuensi 0.9, 1.8 dan 2.1 GHz. Oleh itu, reka bentuk piawai tanpa wayar adalah bagi aplikasi GSM900 , DCS1800 dan W-CDMA. Reka bentuk ini telah dilaksanakan pada proses CMOS 0.13-µm 8-lapisan logam. LNA berbilang piawaian mempamerkan nilai angka hingar (NF) serendah 1.72 dB pada 1.8 GHz dan 1.85 dB pada 2.1 GHz. Gandaan adalah dalam julat 10 ke 11 dB. Titik pintasan tertib ketiga (IIP3) adalah setinggi 0.2 dBm (pada 1.8 GHz), -1 dBm (pada 2.1 GHz) dan -2 dBm (pada 0.9 GHz). Manakala titik mampatan 1 dB pula adalah -12.2 dBm (pada 0.9 GHz), -11.5 dBm (pada 1.8 GHz) dan -11 dBm (pada 2.1 GHz). Jumlah penggunaan kuasa untuk reka bentuk ini adalah 7.42 mW dengan bekalan voltan sebanyak 1.2 V.

# A 0.13-μm CMOS RECONFIGURABLE POWER CONSTRAINED SIMUL-TANEOUS NOISE AND INPUT MATCHING (PCSNIM) LOW NOISE AM-PLIFIER (LNA)FOR MULTI-STANDARD 0.9, 1.8 AND 2.1 GHz MOBILE APPLICATION

#### **ABSTRACT**

The wireless communication industry is experiencing tremendous growth. Previously, multi-standard receivers were designed using parallel architecture to accommodate multiple standards. However, for each path, the area consumption is high which increases cost of fabrication. Responding to the demand for a low-cost and high performance wireless front-end, many intensive researches on CMOS radio-frequency (RF) front-end circuits have been carried out. This project merges the parallel paths into a single path wireless receiver. The ultimate goal is to minimize the trade-off between high performance, smaller size and low-cost at low power consumption design. The target of this project is to design a multi-standard low noise amplifier (LNA) for three standards frequency bands. To demonstrate the effectiveness of the design technique, an LNA design is presented for multi-standard single path LNA with the switching concept. The design can select operating frequency band by switching the switches which are adopted at the input and output matching network. A multi-standard Power Constrained Simultaneous Noise and Input Matching (PCSNIM) topology was implemented. The multi-standard LNA is operated at 0.9, 1.8 and 2.1 GHz frequencies. The design covers wireless standards of GSM900, DCS1800 and W-CDMA applications. The design was implemented on 0.13-µm 8metal CMOS process. The multi-standard LNA shows the noise figure (NF) as low as 1.72 dB at 1.8 GHz and 1.85 dB at 2.1 GHz. The gain is in the range 10 up to 11 dB. The third order intercept point (IIP<sub>3</sub>) is 0.2 dBm (at 1.8 GHz), -1 dBm (at 2.1

GHz) and -2 dBm (at 0.9 GHz) while  $IP_{1dB}$  compression point is -12.2 dBm (at 0.9 GHz), -11.5 dBm (at 1.8 GHz) and -11 dBm (at 2.1 GHz). The power consumption of the design is 7.42 mW with 1.2 V power supply.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Introduction

In the past decade, wireless communication systems have been evolving increasingly, growing rapidly and has high demand in market. The functionality of RF transceiver increase as RF designers pursue cost-effective multi-standard transceivers. Recent developments in wireless communication have new requirements on wireless transceivers. It is desirable to provide multi-band transceiver where wireless standards can operate simultaneously to extend its functionalities (Hashemi, 2002). Various communication standards have to be adopted to accommodate different needs depending on their data rate, bandwidth, operating range and carrier frequency. The key block of a multi-band multi-standard receiver is the low-noise amplifier (LNA). The easiest way is to employ several parallel passages to accommodate the different communication standard. There are different architectures that have been proposed to realize the goal. However, the requirement for a very large design area if the receiver is to be implemented on a single chip. The major drawback would also result in higher production cost. A block diagram of parallel architecture is shown in Figure 1.1.

The parallel architecture, shown in Figure 1.1, utilizes several single-band architectures that are placed in parallel. Each LNA is designed to receive one of the desired bands. The advantage of this architecture is low power consumption. However, for each path, the area consumption is high, which increases the cost of the chip for fab-

rication. One of the challenges for the parallel architecture design is to reduce the area.

Figure 1.1: Block diagram of a multi-band receiver using parallel architecture. (El-Nozahi, 2010).

To overcome the large consumption problem, an architecture that should be more desirable with parallel architecture multi-standard receiver. This architecture can cover various standards with just one single LNA, compared to the previous architecture that uses one LNA for each single standard. Less number of devices leading to a system with less complexity, less area and most importantly, less power consumption.

Figure 1.2: Block diagram of a multi-standard receiver with single LNA (Gustafsson, 2006)

#### 1.2 Motivation

In a multiband LNA, the RF front-end has to cover a huge range of different carrier frequencies to incorporate all the standards. Some front-end needs either wideband LNA (Knapp, 2001), a narrowband LNA with multiple passbands or known also as concurrent LNA (Hashemi, 2002), concurrent with two stages design and wideband multimode (Aravint, 2015) or a tunable LNA (Andersson, 2002).

Concurrent LNAs with multiple passbands are only suitable where the passbands are well separated and not more than two. Tunable LNAs are very attractive but hard to design for a large tuning range (Andersson, 2005). The wideband LNA can receive multiple bands of interest, however, it requires higher consideration on the tradeoff between power, area and sensitivity. The high linearity requirement make it unattractive. Concurrent with two stages; common-gate (CG) and common source (CS) and wideband miltimode can achieve good matching, gain and compression point but the NF is too high up to 8.5 dB (Aravint, 2015).

Tunable LNA which is also known as reconfigurable LNA, can dynamically change its configuration to achieve a different band. By tuning the switches ON/OFF, the LNA can alter between two operating frequencies bands. For this LNA architecture, the number of switchable or tunable components should be limited; otherwise, the performance of the LNA may be deteriorated because of the parasitic parameters introduced by CMOS switches. Furthermore, this topology is generally suitable for narrow band applications. Band selection of the LNA is realize by an inductor tuning circuit. Compared with concurrent LNAs, it can be continuously tuned and is preferred for applications with a large number of frequency bands.