# DESIGN OF FPGA ADDRESS REGISTER IN 28NM PROCESS TECHNOLOGY BASED ON STANDARD CELL BASED APPROACH

By

**CHEW MING CHOO**

A Dissertation submitted for partial fulfillment of the requirement for the degree of Master of Science

July 2013

# Acknowledgement

First and foremost, I would like to express my gratitude to my supervisor, lecturer of Universiti Sains Malaysia, Dr. Bakhtiar Affendi bin Rosdi for the useful comments, remarks and engagement through the learning process of this master thesis.

Furthermore, I would like to thank my manager, Matthew Yap Kean Chin for introducing me to the topic as well for the support on the way.

Finally, I would like to thank my beloved parent for their endless patience and support to me for the entire process. I will be grateful forever for your love.

# **Table of Contents**

| Acknowledgement                                               | ii   |

|---------------------------------------------------------------|------|

| Table of Contents                                             | iii  |

| List of Tables                                                | v    |

| List of Figures and Illustration                              | v    |

| List of Abbreviation and Nomenclature                         | vi   |

| Abstrak                                                       | viii |

| Abstract                                                      | ix   |

| CHAPTER 1 INTRODUCTION                                        | 10   |

| 1.1 Background                                                | 10   |

| 1.2 Problem Statements                                        | 16   |

| 1.3 Research Objectives                                       | 17   |

| 1.4 Scopes                                                    | 18   |

| 1.5 Research Contribution                                     | 18   |

| 1.6 Thesis Organization                                       | 18   |

| CHAPTER 2 LITERATURE REVIEW                                   | 20   |

| 2.1 Introduction                                              | 20   |

| 2.2 FPGA AR                                                   | 20   |

| 2.3 Full custom versus Standard cell based approach           | 22   |

| 2.3.1 Full custom flow                                        | 23   |

| 2.3.2 Design flow for Standard cell based approach            | 24   |

| 2.4 Motivation on standard cell based approach for FPGA AR    | 26   |

| 2.5 Summary                                                   | 27   |

| CHAPTER 3 METHODOLOGY                                         | 28   |

| 3.1 Introduction                                              | 28   |

| 3.2 Handling collateral, design specification and constraints | 30   |

| 3.3 Floorplanning                                             | 31   |

| 3.4 Powerplanning                                             | 32   |

| 3.5 Clock tree synthesis.                                     | 33   |

| 3.6 Placement and Routing                  |

|--------------------------------------------|

| 3.7 Verification                           |

| 3.8 Summary                                |

|                                            |

| CHAPTER 4 RESULTS AND DISCUSSIONS          |

| 4.1 Introduction                           |

| 4.2 Results and Discussions                |

| i) Estimated Design Times                  |

| ii) Area39                                 |

| iii) Delay40                               |

| iv) Power                                  |

| 4.2.1 Collateral handling                  |

| 4.2.2 Floorplanning                        |

| 4.2.3 Powerplanning                        |

| 4.2.4 Clock Tree Synthesis (CTS)           |

| 4.2.5 Placement and Routing                |

| 4.2.6 Verification 49                      |

| i) Formal verification                     |

| ii) Physical verification on LVS and DRC50 |

| iii) IR drop and signal EM50               |

| iv) Static Timing Analysis (STA)           |

| 4.3 Summary                                |

|                                            |

| CHAPTER 5 CONCLUSION AND FUTURE WORKS      |

| 5.1 Conclusion                             |

| 5.2 Future works                           |

|                                            |

| REFERENCES: 59                             |

# **List of Tables**

| TABLE 3-1 FPGA AR GIVEN SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| TABLE 3-2 STANDARD CELL BASED APPROACH STEPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37   |

| TABLE 4-1 COMPARISON OF DESIGN TIMES BETWEEN FULL CUSTOM AND STANDARD CELL BASED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| APPROACHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39   |

| TABLE 4-2 COMPARISON OF THE AREA BETWEEN FULL CUSTOM AND STANDARD CELL BASED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| APPROACHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40   |

| $TABLE\ 4-3\ COMPARISON\ OF\ DELAY\ BETWEEN\ FULL\ CUSTOM\ AND\ STANDARD\ CELL\ BASED\ APPROAGE APPRO$ | CHES |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41   |

| TABLE 4-4 COMPARISON OF POWER CONSUMPTION BETWEEN FULL CUSTOM AND STANDARD CELL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| BASED APPROACHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| TABLE 4-5 THE IR DROP FOR THE POWER AND GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| List of Figures and Illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

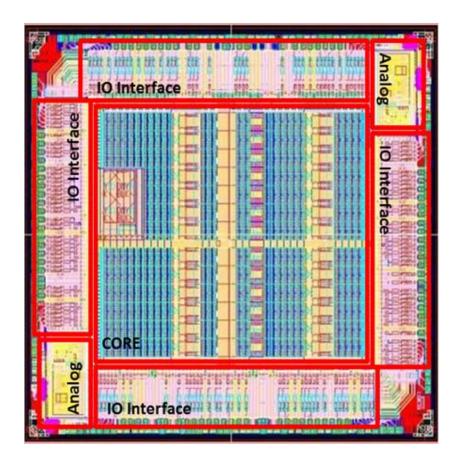

| FIGURE 1-1 THE LAYOUT OF A FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12   |

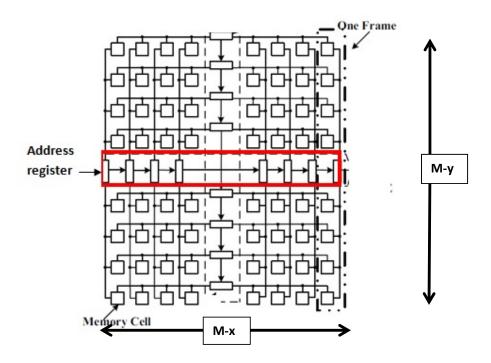

| FIGURE 1-2 FPGA AR IN THE FPGA CORE SECTION, YABIN W. ET.AL (2007)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13   |

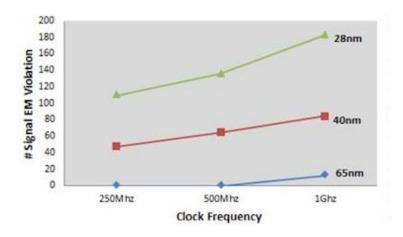

| FIGURE 1-3 SIGNAL EM VIOLATION PLOT USING SAMPLE BLOCK, GEETHA R., ET.AL (2013)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16   |

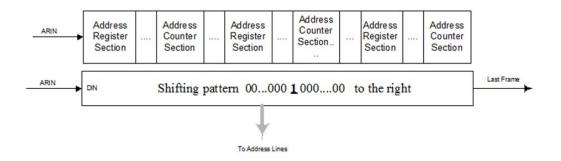

| FIGURE 2-1 OVERVIEW OF AN ADDRESS REGISTER BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21   |

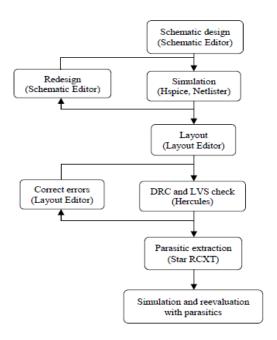

| FIGURE 2-2 FULL CUSTOM DESIGN FLOW CHART, LYONS, E. ET.AL. (2009)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24   |

| FIGURE 2-3 BASIC STANDARD CELL BASED APPROACH, RENOY (2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25   |

| FIGURE 3-1 STANDARD CELL BASED APPROACH FLOW CHART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29   |

| FIGURE 3-2 FLOORPLAN OF FPGA AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32   |

| FIGURE 3-3 AN EXAMPLE OF FISH BONES STRUCTURE FOR THE CLOCK TREE IN FPGA AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33   |

| Figure 4-1 The Layout of FPGA AR created based on standard cell based approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43   |

| FIGURE 4-2 FPGA AR PORTS LOCATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44   |

| Figure 4-3 M3 and M5 pre-route net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45   |

| FIGURE 4-4 M6 AND M5 POWER/GROUND MESH CREATED ON FPGA AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46   |

| Figure 4-5 Clock tree synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47   |

| $Figure\ 4-6\ Location\ of\ antenna\ diode\ and\ isolation\ buffer\ on\ left\ side\ FPGA\ AR$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48   |

| $FIGURE\ 4-7\ Location\ of\ antenna\ diode\ and\ isolation\ buffer\ on\ right\ side\ FPGA\ AR$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48   |

| Figure 4-8 Placement blockage of M3 and M5 being instantiated in FPGA AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48   |

| Figure 4-9 Soft bound for standard cell placement in the middle region of FPGA $\ensuremath{AR}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48   |

| FIGURE 4-10 POST PLACE AND ROUTE LEC RESULT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49   |

| FIGURE 4-11 VIRTUAL PADS SOURCE OF FPGA AR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51   |