# $Al\mbox{-} Ta_2O_5\mbox{-} GaN$ SEMICONDUCTOR DEVICE STRUCTURE

# YEOH LAI SENG

UNIVERSITI SAINS MALAYSIA 2014

# $Al\mbox{-} Ta_2O_5\mbox{-} GaN$ SEMICONDUCTOR DEVICE STRUCTURE

by

### YEOH LAI SENG

Thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

August 2014

#### **ACKNOWLEDGEMENT**

First and foremost, I would like to express my utmost gratitude to the omnipresent God, for answering my prayers and giving me the strength to plod on despite my constitution wanting to give up and throw in the towel. I would not forget my family for their great mental support since the first day I stepped into this research work.

This dissertation would not have been possible without the guidance and the help of several individuals who in one way or another contributed and extended their valuable assistance in the preparation and completion of this study. I would like to pass my deepest appreciation to my supervisor and co-supervisor, namely Prof. Mat Johar bin Abdullah and Prof. Zainuriah binti Hassan, respectively, to their sincerity and encouragement which I will never forget. They have been my inspiration as I hurdle all the obstacles in the completion of this dissertation.

It is my honor to recognize Dr. Naif, who has provided great support to me in performing the time-consuming sputtering process for depositing various oxide thin films on the GaN wafers. Also, thanks for his unselfish and unfailing support for valuable suggestions and comments.

I owe my gratitude to the staff of Nano-Optoelectronics Research (NOR) Lab in Physics School for their supports and guidelines on the equipments operation. They are Cik. Ee Bee Choo, En. Mokhtar, En. Jamil, and En. Azhar. It is a pleasure to thank a couple of NOR Lab research students, to whom I know or not known, in one way or another in keeping me assisted, especially when the system broke down during the course of usage. I also would like to thank the staff from the Institute of Postgraduate Studies (IPS) and the Physics School for being accommodating to my queries and their assistance in student affairs.

I want to convey my thankfulness to a few commercial labs in Bayan Lepas, Penang, for allowing me to use their sophisticated equipments such as OM, FESEM, EDX, FIB, and TIVA systems during my researches. Last but not the least; I would like to show my gratitude to the management team of my current employer, Spansion Penang, for their untiring effort in encouraging me to pursue professional growth. I also appreciate the contributions from some industrial personnel on their valuable insights.

Thank you everyone!

## **TABLE OF CONTENTS**

| Ackn     | owledgement                        | 11     |

|----------|------------------------------------|--------|

| Table    | e of Contents                      | iii    |

| List o   | of Tables                          | vii    |

| List o   | of Figures                         | ix     |

| List o   | of Symbols                         | xviii  |

| List o   | of Abbreviations                   | xxiii  |

| Abstr    | rak                                | xxvii  |

| Abstract |                                    | xxviii |

|          |                                    |        |

| СНА      | PTER 1 – LITERATURE REVIEWS        | 1      |

| 1.1      | Introduction                       | 1      |

| 1.2      | Overview of GaN                    | 1      |

| 1.3      | Research Progress on GaN-Based MOS | 6      |

| 1.4      | Research Issues on GaN-Based MOS   | 9      |

| 1.5      | Introduction to Oxides             | 12     |

| 1.6      | Problem Statement                  | 16     |

| 1.7      | Objective and Scope of Works       | 17     |

| 1.8      | Arrangement of the Thesis          | 18     |

| CHA  | PTER 2 – FUNDAMENTALS OF MOS                  | 19 |

|------|-----------------------------------------------|----|

| 2.1  | Introduction                                  | 19 |

| 2.2  | Explicit Properties of an Ideal MOS           | 19 |

| 2.3  | Energy Band Diagram at Zero Bias              | 20 |

| 2.4  | Energy Band Diagram at Non-Zero Bias          | 21 |

| 2.5  | Semiconductor Electrostatics                  | 23 |

| 2.6  | Gate Voltage Relationship                     | 26 |

| 2.7  | Capacitance-Voltage Characteristic            | 26 |

| 2.8  | Interface Trap and Oxide Charges              | 29 |

| 2.9  | Flat Band Voltage and Flat Band Capacitance   | 30 |

| 2.10 | Optical Property of Gate Oxide                | 33 |

| 2.11 | Current Transport Mechanisms in Gate Oxide    | 34 |

| 2.12 | Resistivity and Conductivity of MOS Structure | 39 |

| 2.13 | Temperature Stress                            | 41 |

| 2.14 | Electrical Stress                             | 42 |

| 2.15 | Visible Light Radiation Stress                | 43 |

| CHA  | PTER 3 – EXPERIMENTAL METHODOLOGIES                                                                                     | 45 |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Introduction                                                                                                            | 45 |

| 3.2  | RCA Cleaning                                                                                                            | 46 |

| 3.3  | Dielectric Sputtering                                                                                                   | 47 |

| 3.4  | Metal Evaporation                                                                                                       | 49 |

| 3.5  | Thermal Annealing                                                                                                       | 51 |

| 3.6  | Filmetric Measurement                                                                                                   | 52 |

| 3.7  | AFM Topographic Analysis                                                                                                | 54 |

| 3.8  | XRD Crystallographic Analysis                                                                                           | 56 |

| 3.9  | XRF Elemental Analysis                                                                                                  | 58 |

| 3.10 | FESEM Micrographic Inspection                                                                                           | 60 |

| 3.11 | EDX Elemental Analysis                                                                                                  | 62 |

| 3.12 | FIB Cross Section                                                                                                       | 64 |

| 3.13 | Four Point Probing                                                                                                      | 67 |

| 3.14 | TIVA Fault Isolation                                                                                                    | 68 |

| 3.15 | C-V & I-V Measurements                                                                                                  | 68 |

|      |                                                                                                                         |    |

| СНА  | PTER 4 – COMPARATIVE STUDIES FOR SiO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> , AND Ta <sub>2</sub> O <sub>5</sub> | 70 |

| 4.1  | Introduction                                                                                                            | 70 |

| 4.2  | Physical and Electrical Properties of As-Grown GaN Wafer                                                                | 70 |

| 4.3  | Physical Properties of As-Sputtered Oxides                                                                              | 74 |

| 4.4  | Optical Properties of As-Sputtered Oxides                                       | 77  |

|------|---------------------------------------------------------------------------------|-----|

| 4.5  | Fundamentals of MOS Structure                                                   | 79  |

| 4.6  | Current Transport Mechanisms in Gate Oxides                                     | 98  |

| 4.7  | Resistivity and Conductivity of MOS Structures                                  | 110 |

| 4.8  | Special Case Study: MOS Performance with SOG as Gate Dielectric                 | 112 |

|      |                                                                                 |     |

| CHA  | APTER 5 – CASE STUDIES ON Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS STRUCTURES | 115 |

| 5.1  | Introduction                                                                    | 115 |

| 5.2  | Effect of Post-Deposition Annealing on MOS Structure                            | 115 |

| 5.3  | Effect of Post-Metallization Annealing on MOS Structure                         | 124 |

| 5.4  | Effect of Substrate Temperature on MOS Structure                                | 133 |

| 5.5  | Effect of Constant Voltage Stress on MOS Structure                              | 142 |

| 5.6  | Effect of Light Radiation on MOS Structure                                      | 152 |

|      |                                                                                 |     |

| CHA  | APTER 6 – CONCLUSION AND FUTURE WORK                                            | 161 |

| 6.1  | Conclusion                                                                      | 161 |

| 6.2  | Future Work                                                                     | 163 |

|      |                                                                                 |     |

| REF  | ERENCES                                                                         | 164 |

| LIST | OF PUBLICATIONS                                                                 | 176 |

## LIST OF TABLES

|            | F                                                                                                                                                                                                                          | Page |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 1.1  | Comparison of properties between $\beta$ -Al $_2$ O $_3$ sapphire and 6H-SiC substrate                                                                                                                                     | 3    |

| Table 1.2  | The properties of various semiconductor materials                                                                                                                                                                          | 4    |

| Table 1.3  | FOM for various semiconductor materials normalized to silicon                                                                                                                                                              | 6    |

| Table 1.4  | Summary of 2003 Semiconductor Roadmap, showing revolution of node, gate length, equivalent oxide thickness of high power (CPU) and low standby power devices (mobile), as well as gate oxide and gate electrode materials. | 10   |

| Table 3.1  | Fabrication process, physical analysis, and electrical analysis in GaN-based MOS project.                                                                                                                                  | 45   |

| Table 4.1  | Physical property of the GaN wafer                                                                                                                                                                                         | 70   |

| Table 4.2  | Electrical property of the GaN wafer                                                                                                                                                                                       | 70   |

| Table 4.3  | Impurities concentration for research grade and commersial grade GaN wafers                                                                                                                                                | 73   |

| Table 4.4  | XRD analysis data for the as-grown GaN wafer                                                                                                                                                                               | 73   |

| Table 4.5  | Topography properties of three different oxides measured by AFM                                                                                                                                                            | 74   |

| Table 4.6  | $(\lambda,\check{R}),m,h\upsilon,v,\check{n},$ and $t_{ox}$ for three different oxides.                                                                                                                                    | 78   |

| Table 4.7  | Preset and actual values of $C_{\text{ox}}$ and $T_{\text{ox}}$ for three different oxides                                                                                                                                 | 79   |

| Table 4.8  | $V_{\text{T}},C_{\text{ox}},C_{\text{min}},\text{and}C_{\text{s}}$ for MOS structures with three different oxides.                                                                                                         | 81   |

| Table 4.9  | Compensated and uncompensated capacitances                                                                                                                                                                                 | 87   |

| Table 4.10 | The values of $N_D$ , $p$ , $\rho$ , and $W_m$ for three different MOS structures.                                                                                                                                         | 89   |

| Table 4.11 | $Q_{\text{sc}},Q_{\text{s}},Q_{\text{n}},E_{\text{ox}},$ and $V_{G}$ for three different MOS structures.                                                                                                                   | 92   |

| Table 4.12 | $C_{FB}$ and $V_{FB}$ values for three different MOS structures                                                                                                                                                            | 92   |

| Table 4.13 | $N_{f},Q_{f},\text{and}\Delta V_{G}(\text{fixed charge})$ for three different MOS structures                                                                                                                               | 93   |

| Table 4.14 | Min. $D_{it},E_{it},Q_{it},$ and $\Delta V_G$ (interface trap) for three different MOS structures.                                                                                                                         | 95   |

| Table 4.15 | Literature data of $N_{\rm f}$ and $D_{\rm it}$ for GaN-based MOSs                                                                                                                                                         | 95   |

| Table 4.16 | Evaluation data for Ohm's conduction in three different gate oxides                                                                                                                                                        | 102  |

| Table 4.17 | $N_t$ , $\mu$ , and $n_0$ for three different MOS structures                                                                                                                                                               | 102  |

| Table 4.18 | Evaluation data for F-N tunneling in MOS structures with three different gate oxides                                                                             | 105 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.19 | Evaluation data for P-F emission in MOS structures with three different gate oxides                                                                              | 105 |

| Table 4.20 | Evaluation data for Schottky emission in MOS structures with three different gate oxides                                                                         | 109 |

| Table 4.21 | Evaluation data for FAT in MOS structures with three different gate oxides                                                                                       | 110 |

| Table 4.22 | Dynamic resistivity, dynamic conductivity, and electric field strength of three different MOS structures.                                                        | 110 |

| Table 5.1  | Effect of PDA temperatures on the Ga-to-N ratio                                                                                                                  | 121 |

| Table 5.2  | Effect of PDA temperatures on the Ta-to-O ratio                                                                                                                  | 121 |

| Table 5.3  | $\lambda,C_{ox},C_{FB},V_{FB},\Delta V_{FB},k_{ox},$ and $N_f$ at various substrate temperatures.                                                                | 137 |

| Table 5.4  | $\epsilon_{d}$ and $\check{n}$ values extracted from the P-F plots at various substrate temperatures                                                             | 140 |

| Table 5.5  | Gate current with its incremetal percentage, and maximum defect density for different stressing voltages                                                         | 143 |

| Table 5.6  | Validation of current conduction mechanism at different stressing voltages                                                                                       | 147 |

| Table 5.7  | $\Delta J/J_o$ at various gate voltages                                                                                                                          | 148 |

| Table 5.8  | $ \Delta J/J_o $ @ $V_G = -3 V$ at various $V_S$                                                                                                                 | 150 |

| Table 5.9  | $\lambda$ , P, hv, $\Phi_o$ , and $\phi$ for five different visible lights                                                                                       | 152 |

| Table 5.10 | $\Phi$ , $E_A$ , $E_D$ , and $E_A/\Phi$ for five different visible lights.                                                                                       | 153 |

| Table 5.11 | $C_{ox}$ and $C_{min}$ of an Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure radiated with visible light sources from red to cyan in sequence               | 155 |

| Table 5.12 | $C_{ox}$ , $C_{min}$ , and $k_{ox}$ of an Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure radiated with visible light sources from cyan to red in sequence. | 156 |

| Table 5.13 | Extracted I and $R_S$ at $V_G = 5$ V for an Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure radiated with different visible light sources                   | 159 |

### LIST OF FIGURES

|             |                                                                                                                                     | Page |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Wurtzite unit cell                                                                                                                  | 2    |

| Figure 1.2  | Wurtzite structure                                                                                                                  | 2    |

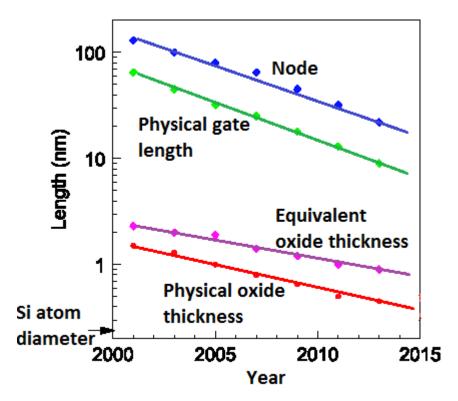

| Figure 1.3  | The scaling of feature size, gate length, and oxide thickness from year 2000 to year 2015 according to 2003 Semiconductors Roadmap. | 10   |

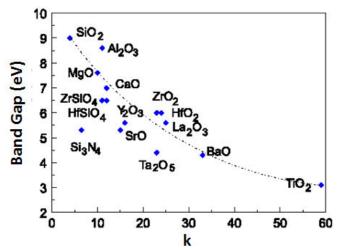

| Figure 1.4  | Band gap versus dielectric constant for various insulators                                                                          | 13   |

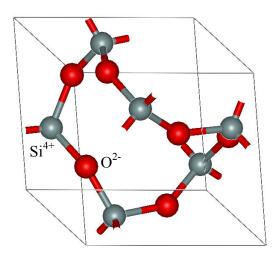

| Figure 1.5  | Ball-and-stick model for the crystal structure of $\alpha\text{-quartz SiO}_2$                                                      | 14   |

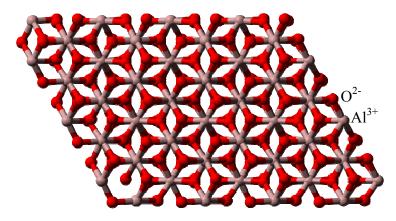

| Figure 1.6  | Ball-and-stick model of part of the crystal structure of $\alpha\text{-Al}_2O_3$                                                    | 15   |

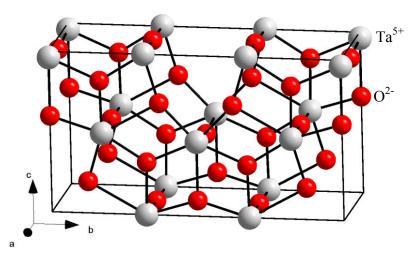

| Figure 1.7  | Ball-and-stick model of part of the crystal structure of Ta <sub>2</sub> O <sub>5</sub>                                             | 16   |

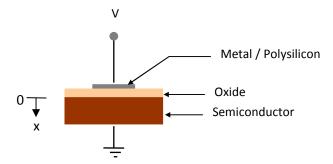

| Figure 2.1  | Cross sectional view of a MOS structure                                                                                             | 19   |

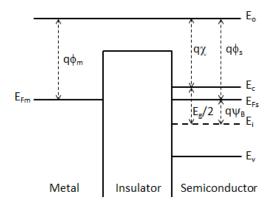

| Figure 2.2  | Energy band diagram of an ideal n-type MOS at $V_G = 0$                                                                             | 20   |

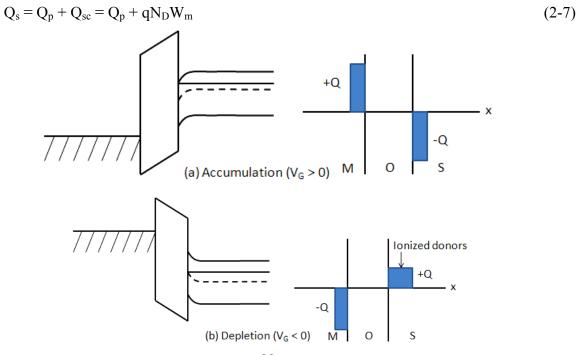

| Figure 2.3  | Energy band diagrams and charge distributions of an ideal n-type MOS at $V_G \neq 0$                                                | 23   |

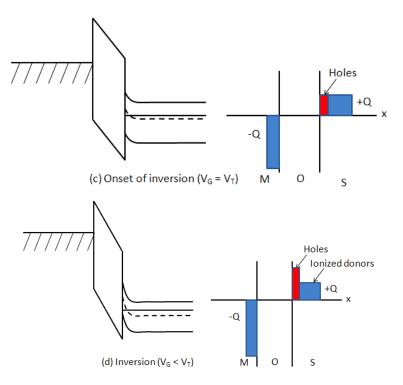

| Figure 2.4  | Energy band diagram at the surface of an n-type MOS                                                                                 | 24   |

| Figure 2.5  | The high and low frequencies C-V characteristics of an n-type MOS                                                                   | 27   |

| Figure 2.6  | (a) Equivalent 3-element model of MOS structure in strong accumulation (b) Simplified model used to determine $R_{\rm S}$           | 28   |

| Figure 2.7  | The basic classification of oxide charges                                                                                           | 30   |

| Figure 2.8  | Effect of a sheet charge in oxide (a) $V_G = 0$ (b) Flat band condition                                                             | 31   |

| Figure 2.9  | Effect of oxide charges and interface traps on C-V curve of a MOS structure                                                         | 32   |

| Figure 2.10 | Interaction of oxide-semiconductor structure with light beams where $\check{n}_1{<}\:\check{n}_2{<}\:\check{n}_3$                   | 34   |

| Figure 2.11 | Four current transport mechanisms in MOS structure                                                                                  | 35   |

| Figure 2.12 | Non-linear current as a function of applied voltage                                                                                 | 40   |

| Figure 3.1  | Flow chart of fabrication and characterization works in GaN-based MOS project                                                                                                    | 45 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2  | Schematic diagram of a fume hood for RCA cleaning process                                                                                                                        | 47 |

| Figure 3.3  | Illustration of sputtering process                                                                                                                                               | 48 |

| Figure 3.4  | Schematic diagram of a sputtering machine                                                                                                                                        | 49 |

| Figure 3.5  | Schematic diagram of a high-vacuum filament evaporator                                                                                                                           | 50 |

| Figure 3.6  | Schematic diagram of an annealing furnace                                                                                                                                        | 52 |

| Figure 3.7  | Working principles of spectroscopic ellipsometry (left) and spectral reflectance (right)                                                                                         | 53 |

| Figure 3.8  | Reflectance and transmission of light in three different materials (left) and in non-absorbing material (right)                                                                  | 54 |

| Figure 3.9  | Schematic diagram of a contact mode AFM                                                                                                                                          | 56 |

| Figure 3.10 | Illustration of an x-ray diffraction experiment                                                                                                                                  | 57 |

| Figure 3.11 | Schematic representation of diffraction of X-rays in a crystalline material. Bragg's law is satisfied when the path length difference of the x-rays (green) equals to $n\lambda$ | 57 |

| Figure 3.12 | Orbital structure of an atom                                                                                                                                                     | 59 |

| Figure 3.13 | Schematic of an x-ray tube                                                                                                                                                       | 59 |

| Figure 3.14 | Type of signals generated from electron beam in a SEM                                                                                                                            | 61 |

| Figure 3.15 | Schematic diagram of a SEM                                                                                                                                                       | 62 |

| Figure 3.16 | The principle of EDX operation                                                                                                                                                   | 63 |

| Figure 3.17 | The interaction volumes for thin foil and bulk specimen                                                                                                                          | 64 |

| Figure 3.18 | Schematic diagram of a FIB system                                                                                                                                                | 65 |

| Figure 3.19 | Operating principle of FIB                                                                                                                                                       | 66 |

| Figure 3.20 | (Left) Four-point measurement of resistance between voltage sense at connections 2 and 3. Current is supplied through force connections 1 and 4. (Right) Internal circuitry of four point probe. | 67 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.21 | A typical simultaneous C-V measurement for a n-type semiconductor of a MOS structure                                                                                                             | 69 |

| Figure 3.22 | The block diagram of a basic C-V measurement setup                                                                                                                                               | 6  |

| Figure 4.1  | Appearance of the as-grown GaN-on-sapphire wafer                                                                                                                                                 | 7  |

| Figure 4.2  | Optical image of the as-grown GaN surface (50x)                                                                                                                                                  | 71 |

| Figure 4.3  | FESEM micrograph of the as-grown GaN surface (50x)                                                                                                                                               | 71 |

| Figure 4.4  | Two dimensional AFM image of surface topography for the as-grown GaN wafer                                                                                                                       | 71 |

| Figure 4.5  | Three dimensional AFM image of surface topography for the as-grown GaN wafer                                                                                                                     | 71 |

| Figure 4.6  | EDX spectrum of the as-grown GaN wafer                                                                                                                                                           | 72 |

| Figure 4.7  | XRF spectrum of the as-grown GaN wafer                                                                                                                                                           | 72 |

| Figure 4.8  | XRD spectrum of the as-grown GaN wafer                                                                                                                                                           | 73 |

| Figure 4.9  | Two-dimensional AFM image of the SiO <sub>2</sub> surface topography                                                                                                                             | 74 |

| Figure 4.10 | Three-dimensional AFM image of the SiO <sub>2</sub> surface topography                                                                                                                           | 74 |

| Figure 4.11 | Two-dimensional AFM image of the Al <sub>2</sub> O <sub>3</sub> surface topography                                                                                                               | 75 |

| Figure 4.12 | Three-dimensional AFM image of the Al <sub>2</sub> O <sub>3</sub> surface topography                                                                                                             | 75 |

| Figure 4.13 | Two-dimensional AFM image of the Ta <sub>2</sub> O <sub>5</sub> surface topography                                                                                                               | 75 |

| Figure 4.14 | Three-dimensional AFM image of the Ta <sub>2</sub> O <sub>5</sub> surface topography                                                                                                             | 75 |

| Figure 4.15 | FESEM micrograph of the SiO <sub>2</sub> surface morphology                                                                                                                                      | 75 |

| Figure 4.16 | FESEM micrograph of the Al <sub>2</sub> O <sub>3</sub> surface morphology                                                                                                                        | 75 |

| Figure 4.17 | FESEM micrograph of the Ta <sub>2</sub> O <sub>3</sub> surface morphology                                                                                                                        | 76 |

| Figure 4.18 | EDX spectrum of SiO <sub>2</sub> deposited on GaN                                                                                                                   | 76 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.19 | EDX spectrum of Al <sub>2</sub> O <sub>3</sub> deposited on GaN                                                                                                     | 76 |

| Figure 4.20 | EDX spectrum of Ta <sub>2</sub> O <sub>3</sub> deposited on GaN                                                                                                     | 77 |

| Figure 4.21 | The plot of reflectance vs. wavelength for SiO <sub>2</sub> deposited on GaN                                                                                        | 78 |

| Figure 4.22 | The plot of reflectance vs. wavelength for Al <sub>2</sub> O <sub>3</sub> deposited on GaN                                                                          | 78 |

| Figure 4.23 | The plot of reflectance vs. wavelength for Ta <sub>2</sub> O <sub>5</sub> deposited on GaN                                                                          | 79 |

| Figure 4.24 | The applied a.c. and d.c. voltages during C-V sweep measurement                                                                                                     | 80 |

| Figure 4.25 | High-frequency C-V characteristic of the Al/SiO <sub>2</sub> /GaN MOS structure                                                                                     | 81 |

| Figure 4.26 | High-frequency C-V characteristic of the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure                                                                       | 82 |

| Figure 4.27 | High-frequency C-V characteristic of the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                       | 82 |

| Figure 4.28 | Charge distribution in n-type MOS under d.c. biasing condition corresponding to accumulation                                                                        | 83 |

| Figure 4.29 | Charge distribution in n-type MOS under d.c. biasing condition corresponding to depletion                                                                           | 84 |

| Figure 4.30 | Charge distribution in n-type MOS under d.c. biasing condition corresponding to inversion when $\omega \to 0$                                                       | 85 |

| Figure 4.31 | Charge distribution in n-type MOS under d.c. biasing condition corresponding to inversion when $\omega \to \infty$                                                  | 85 |

| Figure 4.32 | Cross-sectional diagram of MOS structure fabricated in this work                                                                                                    | 87 |

| Figure 4.33 | Compensated capacitance ( $C_{ADJ}$ ) and uncompensated capacitance ( $C$ ) as a function of gate bias for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure | 87 |

| Figure 4.34 | Compensated capacitance ( $C_{ADJ}$ ) and uncompensated capacitance ( $C$ ) as a function of gate bias for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure | 88 |

| Figure 4.35 | Doping concentration in GaN wafer as a function of depletion depth for the $Al/SiO_2/GaN$ MOS structure. The maximum depletion layer width $W_m$ is 370 $\mu m$ .   | 89 |

| Figure 4.36 | Doping concentration in GaN wafer as a function of depletion depth for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure. The maximum depletion layer width $W_m$ is 0.02 $\mu m$ . | 90  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.37 | Doping concentration in GaN wafer as a function of depletion depth for the Al/Ta $_2O_5$ /GaN MOS structure. The maximum depletion layer width $W_m$ is 0.6 $\mu m$ .                      | 90  |

| Figure 4.38 | Equilibrium energy band diagram for n-type GaN MOS                                                                                                                                         | 91  |

| Figure 4.39 | Filling of interface levels during (a) inversion (b) depletion (c) accumulation in an n-type GaN-based MOS                                                                                 | 93  |

| Figure 4.40 | Interface trap density as a function of gate voltage for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS                                                                                    | 94  |

| Figure 4.41 | Interface trap density as a function of surface potential for the Al/SiO <sub>2</sub> /GaN MOS structure                                                                                   | 95  |

| Figure 4.42 | Interface trap density as a function of surface potential for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure                                                                     | 96  |

| Figure 4.43 | Interface trap density as a function of surface potential for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                     | 96  |

| Figure 4.44 | Interface trap density as a function of interface trap energy for the Al/SiO <sub>2</sub> /GaN MOS structure                                                                               | 97  |

| Figure 4.45 | Interface trap density as a function of interface trap energy for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure                                                                 | 97  |

| Figure 4.46 | Interface trap density as a function of interface trap energy for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                 | 98  |

| Figure 4.47 | Leakage current as a function of gate voltage for MOS structures with different gate oxides                                                                                                | 99  |

| Figure 4.48 | Current density (in LN scale) vs. gate voltage for MOS structures with different gate oxides                                                                                               | 100 |

| Figure 4.49 | Leakage current density as a function of gate voltage with different current transport mechanisms for the Al/SiO <sub>2</sub> /GaN MOS structure                                           | 100 |

| Figure 4.50 | Leakage current density as a function of gate voltage with different current transport mechanisms for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure                             | 101 |

| Figure 4.51 | Leakage current density as a function of gate voltage with different current transport mechanisms for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure | 101 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.52 | ln (J/E <sup>2</sup> ) vs. 1/E for the Al/SiO <sub>2</sub> /GaN MOS structure                                                                                  | 103 |

| Figure 4.53 | ln (J/E <sup>2</sup> ) vs. 1/E for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure                                                                    | 104 |

| Figure 4.54 | ln (J/E <sup>2</sup> ) vs. 1/E for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                    | 104 |

| Figure 4.55 | ln (J/E) vs. E <sup>1/2</sup> for the Al/SiO <sub>2</sub> /GaN MOS structure                                                                                   | 106 |

| Figure 4.56 | ln (J/E) vs. E <sup>1/2</sup> for the Al/Al <sub>2</sub> O <sub>3</sub> /GaN MOS structure                                                                     | 106 |

| Figure 4.57 | $ln (J/E) vs. E^{1/2}$ for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                            | 107 |

| Figure 4.58 | $ln (J/T^2)$ vs. $E^{1/2}$ for the Al/SiO <sub>2</sub> /GaN MOS structure                                                                                      | 108 |

| Figure 4.59 | $ln (J/T^2)$ vs. $E^{1/2}$ for the $Al/Al_2O_3/GaN$ MOS structure                                                                                              | 108 |

| Figure 4.60 | $ln (J/T^2)$ vs. $E^{1/2}$ for the $AlTa_2O_5/GaN$ MOS structure                                                                                               | 109 |

| Figure 4.61 | Dynamic resistivity vs. gate voltage for MOS structures with different gate oxides                                                                             | 111 |

| Figure 4.62 | Dynamic conductivity vs. gate voltage for MOS structures with different gate oxides                                                                            | 111 |

| Figure 4.63 | EDX analysis result for the as-spun SOG on GaN                                                                                                                 | 112 |

| Figure 4.64 | C-V plot of the Al/SOG/GaN MOS structure                                                                                                                       | 113 |

| Figure 4.65 | I-V plot of the Al/SOG/GaN MOS structure                                                                                                                       | 114 |

| Figure 4.66 | Optical image of the annealed-SOG film (50x)                                                                                                                   | 114 |

| Figure 4.67 | FESEM micrograph of the annealed-SOG film (500x)                                                                                                               | 114 |

| Figure 5.1  | FESEM micrograph of surface morphology of an as-deposited Ta <sub>2</sub> O <sub>5</sub> film on GaN wafer (50kx)                                              | 116 |

| Figure 5.2  | FESEM micrograph of surface morphology of a $Ta_2O_5$ film on GaN wafer annealed at 250 °C (50kx)                                                              | 116 |

| Figure 5.3  | FESEM micrograph of surface morphology of a Ta <sub>2</sub> O <sub>5</sub> film on GaN wafer annealed at 500 °C (50kx)                                         | 116 |

| Figure 5.4  | Figure 5.4 FESEM micrograph of surface morphology of a Ta <sub>2</sub> O <sub>5</sub> film on GaN wafer annealed at 750 °C (50kx) |     |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Figure 5.5  | FESEM micrograph of surface morphology of a $Ta_2O_5$ film on GaN wafer annealed at 1000 °C (50kx)                                | 116 |  |  |

| Figure 5.6  | Incremental of the Ta <sub>2</sub> O <sub>5</sub> grain size with PDA temperature                                                 | 117 |  |  |

| Figure 5.7  | XRD profiles of the as-deposited and the annealed oxide films                                                                     | 118 |  |  |

| Figure 5.8  | Dependence of C-V characteristic on the PDA temperature for the Al/ $Ta_2O_5$ /GaN MOS structure                                  | 119 |  |  |

| Figure 5.9  | Proportional increase of Cox and k with Tanneal                                                                                   | 120 |  |  |

| Figure 5.10 | Dependence of ${D_{it}}^m$ on the PDA temperature for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                    | 122 |  |  |

| Figure 5.11 | Dependence of I-V characteristic on the PDA temperature for the Al/ $Ta_2O_5/GaN$ MOS structure                                   | 123 |  |  |

| Figure 5.12 | Dependence of I-V characteristic on the PMA temperature for the Al/Ta $_2O_5$ /GaN MOS structure                                  | 124 |  |  |

| Figure 5.13 | Dependence of C-V characteristic on the PMA temperature for the Al/Ta $_2$ O $_5$ /GaN MOS structure                              | 125 |  |  |

| Figure 5.14 | Re-plot of C-V curve at 250 °C on a separate scale                                                                                | 126 |  |  |

| Figure 5.15 | Optical image of the Al gate electrode after PMA at 750 °C (50x)                                                                  | 127 |  |  |

| Figure 5.16 | Close-up optical view at area X on the Al gate electrode (1kx)                                                                    | 127 |  |  |

| Figure 5.17 | FESEM image of the Al gate electrode after PMA at 750 °C (60x)                                                                    | 127 |  |  |

| Figure 5.18 | Enlarged FESEM image at area Y on the Al gate electrode (150x)                                                                    | 127 |  |  |

| Figure 5.19 | Surface morphology at the electrode center. There were plenty of blemishes on the electrode surface (3kx)                         | 127 |  |  |

| Figure 5.20 | Surface morphology at the electrode edge. The surface was smooth and there was no blemish formation (3kx).                        | 127 |  |  |

| Figure 5.21 | EDX spectrum of oxidixed Al pad                                                                                                   | 128 |  |  |

| Figure 5.22 | EDX spectrum of a normal Al pad                                                                                                                                                           | 128 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.23 | Infrared image with indication of current leakage on the MOS structure                                                                                                                    | 129 |

| Figure 5.24 | Overlay of infrared image with electrode image, showing that leakage occurred along the ring defect on the MOS structure.                                                                 | 129 |

| Figure 5.25 | FIB-cut at X-Y direction on the ring defect (10kx)                                                                                                                                        | 131 |

| Figure 5.26 | FIB cross-sectional view at X-Y plane, showing migration of Al dendrites into GaN in the vicinity of the TIVA site. The migration left behind vacancies in the Al gate electrode (250kx). | 131 |

| Figure 5.27 | Close-up view on the structure of Al dendrite                                                                                                                                             | 132 |

| Figure 5.28 | There was no Al vacancy in the gate electrode at non-TIVA site (200kx)                                                                                                                    | 132 |

| Figure 5.29 | High-frequency C-V curves for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure at different substrate temperatures                                                                | 134 |

| Figure 5.30 | C-V curves of normalized capacitances for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure at different substrate temperatures                                                    | 134 |

| Figure 5.31 | $V_{FB}$ and $\Delta V_{FB}$ as a function of $T$                                                                                                                                         | 136 |

| Figure 5.32 | $V_{FB}$ and $\Delta V_{FB}$ as a function of 1000/T                                                                                                                                      | 136 |

| Figure 5.33 | I-V curves for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure at different substrate temperatures                                                                               | 138 |

| Figure 5.34 | I-V curves (in ln scale) for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure at different substrate temperatures                                                                 | 138 |

| Figure 5.35 | P-F plots for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure at different substrate temperatures                                                                                | 140 |

| Figure 5.36 | Mid-gap interface trap density versus surface potential for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure at different substrate temperatures                                  | 141 |

| Figure 5.37 | I-V characteristic as a function of stressing voltage for the $Al/Ta_2O_5/GaN$ MOS structure                                                                                              | 144 |

| Figure 5.38 | J-V characteristic as a function of stressing voltage for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                        | 144 |

| Figure 5.39 | I-V characteristic (in log scale) as a function of stressing voltage for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                          | 145 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.40 | Poole-Frenkel plot at various stressing voltages                                                                                                                                                           | 146 |

| Figure 5.41 | Schottky emission plot at various stressing voltages                                                                                                                                                       | 146 |

| Figure 5.42 | I-V characteristic as a function of stressing time for the $Al/Ta_2O_5/GaN\ MOS\ structure$                                                                                                                | 147 |

| Figure 5.43 | $\Delta J/J_o$ as a function of stressing voltage for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                                             | 149 |

| Figure 5.44 | $\Delta J/J_o$ versus $Q_{inj}$ as a function of gate voltage                                                                                                                                              | 149 |

| Figure 5.45 | C-V characteristic as a function of stressing voltage for the $Al/Ta_2O_5/GaN\ MOS\ structure$                                                                                                             | 151 |

| Figure 5.46 | Normalized capacitance for the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure                                                                                                                        | 151 |

| Figure 5.47 | Light dependence of HF-CV characteristics for the Al/ $Ta_2O_5$ /GaN MOS structure. The radiation sequence is from red to cyan.                                                                            | 154 |

| Figure 5.48 | Light dependence of HF-CV characteristics for the Al/ $Ta_2O_5$ /GaN MOS structure. The radiation sequence is from cyan to red.                                                                            | 155 |

| Figure 5.49 | Time-dependent of the C-V characteristic of the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure under illumination of cyan light                                                                      | 157 |

| Figure 5.50 | Time-dependent of the C-V characteristic of the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure under illumination of cyan light. The minus sign (-) indicates removal of light for a certain period. | 157 |

| Figure 5.51 | Light dependence of I-V characteristics in the Al/Ta <sub>2</sub> O <sub>5</sub> /GaN MOS structure. The radiation sequence is from red to cyan.                                                           | 160 |

| Figure 5.52 | Mid-gap interface trap density versus surface potential as a function of visible light wavelength                                                                                                          | 160 |

#### LIST OF SYMBOLS

α Absorption coefficient

A Cross-sectional area of gate in MOS structure

c Speed of light in free space

č Capture cross section

C Total capacitance

C<sub>ADJ</sub> Series resistance compensated parallel model capacitance

C<sub>FB</sub> Flat band capacitance

C<sub>min</sub> Minimum capacitance

C<sub>ox</sub> Oxide capacitance

C<sub>s</sub> Semiconductor depletion layer capacitance

D Dielectric displacement

D<sub>it</sub> Interface trap density

D<sub>it</sub> m Mid-gap interface trap density

D<sub>n</sub> Electron diffusivity

D<sub>total</sub> Total interface trap density

Đ<sub>total</sub> Total transmission coefficient

$\varepsilon_d$  Dynamic dielectric constant

$\varepsilon_{o}$  Vacuum permittivity

$\varepsilon_{\rm r}$  Relative permittivity

$\varepsilon_{\rm s}$  Semiconductor permittivity

E Electric field strength

E<sub>c</sub> Bottom of conduction band

E<sub>F</sub> Fermi level

E<sub>g</sub> Energy band gap

E<sub>i</sub> Intrinsic Fermi level

E<sub>o</sub> Minimum energy where an electron must have to reach vacuum level

E<sub>OT</sub> Equivalent oxide thickness

E<sub>ox</sub> Electric field in oxide

E<sub>s</sub> Electric field in semiconductor

E<sub>v</sub> Top of valance band

f Frequency

G Conductance

G<sub>ADJ</sub> Series resistance compensated conductance

h Plank's constant

h Reduced Plank's constant

I Current

J Current density

J<sub>child</sub> Child's law current density

J<sub>DT</sub> Direct tunneling current density

J<sub>FAT</sub> Field-assited tunneling current density

J<sub>FN</sub> Fowler-Nordheim tunneling current density

J<sub>g</sub> Post-stress current density

J<sub>o</sub> Pre-stress current density

J<sub>Ohm</sub> Ohm's current density

J<sub>PF</sub> Poole-Frenkel emission current density

J<sub>SE</sub> Schottky emission current density

J<sub>TAT</sub> Trap-assited tunneling current density

J<sub>TFL</sub> Trap-filled limited current density

$\Delta J/J_o$  Defect density created by constant voltage stress

k Extinction coefficient

k<sub>B</sub> Boltzmann constant

k<sub>ox</sub> Dielectric constant of oxide

$\kappa$  Wave vector in a medium with wavelength  $\lambda$

$\kappa_o$  Wave vector in free space with wavelength  $\lambda_o$

$\kappa_{ox}$  Wave vector in oxide

m<sub>o</sub> Electron rest mass

m<sub>n</sub> Electron effective mass

m<sub>p</sub> Hole effective mass

m<sub>ox</sub>\* Effective mass of electron in oxide

n Concentration of free electrons

ň Reflective index

n<sub>bulk</sub> Electron concentration in the bulk of non-degenerate semiconductor

n<sub>i</sub> Intrinsic carrier concentration

n<sub>n</sub> Electron concentration in n-type semiconductor

n<sub>o</sub> Density of thermal generated free carriers

n<sub>s</sub> Electron concentration at semiconductor surface

N Flux of metal electrons

N<sub>A</sub> Acceptor impurity density

N<sub>D</sub> Donor impurity density

N<sub>f</sub> Fixed oxide charges density

N<sub>T</sub> Total trap density in oxide

p Concentration of free holes

p<sub>bulk</sub> Hole concentration in the bulk of non-degenerate semiconductor

p<sub>n</sub> Hole concentration in n-type semiconductor

p<sub>s</sub> Hole concentration at semiconductor surface

ρ Charge density per unit volume

$\rho_s$  Surface charge density per unit volume

b Resistivity

b<sub>d</sub> Dynamic resistivity

P Radiometric power

P<sub>g</sub> Defect generation rate

q Electronic charge

$q\phi_m$  Work function of metal

$q\phi_s$  Work function of semiconductor

$q\phi_{ms}$  Work function difference between metal and semiconductor

qχ Electron affinity

$q\Psi_B$  Energy difference between Fermi level and intrinsic Fermi level

Q<sub>f</sub> Fixed oxide charges

Q<sub>inj</sub> Injected charges

Q<sub>it</sub> Interface trapped charges

Q<sub>m</sub> Mobile ionic charges

Q<sub>M</sub> Charges placed on gate

Q<sub>ot</sub> Oxide trapped charges

Q<sub>ox</sub> Positive sheet charges per unit area in oxide

Q<sub>p</sub> Charges in inversion layer

Q<sub>s</sub> Charges per unit area in semiconductor

Q<sub>sc</sub> Charges in depletion layer

r Compensation factor

r<sub>d</sub> Dynamic resistance

R Resistance

Ř Reflectance

R<sub>S</sub> Series resistance

R<sub>Sh</sub> Sheet resistance

S<sub>Ohm</sub> Gradient of logarithm J-V plot in Ohm's conduction

t Time

t<sub>ox</sub> Oxide thickness

$\tau_e$  Electron transit time

T Absolute temperature

T<sub>c</sub> Characteristic temperature related to trap distribution

$\mu_n$  Electron mobility

v Phase velocity of light wave

υ Frequency of light wave

V Voltage

V<sub>FB</sub> Flat band voltage

V<sub>G</sub> d.c. bias on gate

V<sub>o</sub> Potential across oxide

V<sub>on</sub> Crossover voltage where Ohm's law transits to Child's law

V<sub>S</sub> Stressing voltage

V<sub>T</sub> Gate threshold voltage at the onset of strong inversion

V<sub>TFL</sub> Threshold voltage of trap-filled limited process

ω Angular frequency

W Depletion layer width

W<sub>m</sub> Maximum width of depletion region

Z Charge of center in Poole-Frenkel emission

σ Electrical conductivity

$\sigma_d$  Dynamic conductivity

λ Light wavelength in a medium

$\lambda_0$  Light wavelength in free space

$\lambda_{Debve}$  Extrinsic Debye length

φ<sub>o</sub> Triangular barrier height in Fowler-Nordheim tunneling

φ Fluence

$\phi_{\rm B}$  Barrier height between semiconductor and oxide

$\phi_{\rm F}$  Electrostatic potential of semiconductor

$\phi_{ox}$  Metal-oxide barrier

Φ<sub>PF</sub> Barrier lowering associated with Coulomb potential in Poole-Frenkel emission

Φ<sub>t</sub> Energy barrier separating traps from conduction band in Poole-Frenkel emission

$\Delta \phi$  Conduction band offset between oxide and oxide-semiconductor interface

$\Phi_0$  Photon flux

$\Psi(x)$  Electrostatic potential inside semiconductor at a given point x

Ψ<sub>B</sub> Potential difference between Fermi level and intrinsic Fermi level

$\Psi_s$  Surface potential at x = 0

$\Psi_{\rm s}$  (inv) Surface potential at strong inversion

$\theta$  X-ray diffraction angle

#### LIST OF ABBREVIATIONS

a. c. Alternating current

a. u. Arbitrary unit

AFM Atomic force microscope

Ag Silver

Al Aluminium

AlN Aluminium nitride Al<sub>2</sub>O<sub>3</sub> Aluminium oxide

Ar Argon

Au Gold

BFOM Baliga figure-of-merit

BHFFOM Baliga high-frequency figure-of-merit

BOE Buffer oxide etch

BSE Back-scattered electron

C Carbon

Ca Calcium

CaO Calcium oxide

Cd Cadmium

CMOS Complementary metal-oxide-semiconductor

Co Cobalt

Cr Chromium

Cu Copper

C-V Capacitance-voltage

CVS Constant voltage stress

d.c. Direct current

DFT Density functional theory

DI Deionized

DRAM Dynamic random access memory

DUT Device-under-test

ECR Electron cyclotron resonance

EDX Energy dispersive x-ray

ELOG Epitaxial lateral overgrowth

FAT Field-assited tunneling

FEG Field emission gun

FESEM Field emission scanning electron microscope

FIB Focused ion beam FN Fowler-Nordheim

FOM Figure-of-merit

FWHM Full width at half maximum

G Gate

GaN

GaAs Gallium arsenide GaCl<sub>3</sub> Gallium chloride

Ga<sub>2</sub>O<sub>3</sub> Gallium oxide

GaP Gallium phosphite

GPIB General purpose interface bus

Gallium nitride

H Hydrogen

HBT Heterojunction bipolar transistor

HCl Hydrochloric acid / hydrogen chloride

HEMT High electron mobility transistor

HF Hydrofluoric acid

HFET Heterojunction field effect transistor

HNO<sub>3</sub> Nitric acid

H<sub>2</sub>O Water

H<sub>3</sub>PO<sub>4</sub> Phosphoric acid

HVPE Hydride vapor phase epitaxy

ICS Interactive characterization software

InP Indium phosphide

I-V Current-voltage

JFOM Johnson figure-of-merit

KFOM Keyes figure-of-merit

LaB<sub>6</sub> Lanthanum hexaboride

LED Light emitting diode

LEEBI Low energy electron beam irradiation

Li Lithium

LMIS Liquid-metal ion sources

MBE Molecular beam epitaxy

MCA Multi channel analyzer

MESFET Metal-semiconductor field effect transistor

Mg Magnesium

MgO Magnesium oxide

MISFET Metal-insulator-semiconductor field effect transistor

MOCVD Metal-organic chemical vapor deposition

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field effect transistor

NH<sub>3</sub> Ammonia

NH<sub>4</sub>OH Ammonium hydroxide

Ni Nickel

OBIC Optical beam induced current

PDA Post-deposition annealing

PF Poole-Frenkel

PMA Post-metallization annealing

PSD Position sensitive detector

Pt Platinum

PVD Physical vapor deposition

QB Quasi-breakdown

RCA Radio Corporation of America

RF Radio-frequency

RHEED Reflection high-energy electron diffraction

RMS Root mean square

RPECVD Remote plasma-enhanced chemical vapor deposition

SC Standard cleaning

SCL Space charge limited

Sc<sub>2</sub>O<sub>3</sub> Scandium oxide

S-D Source-drain

SE Spectroscopic ellipsometry

SEI Seebeck effect imaging

SEM Scanning electron microscope

Si Silicon

SiC Silicon carbide

SILC Stress-induced leakage current

Si<sub>3</sub>N<sub>4</sub> Silicon nitride

SiO<sub>2</sub> Silicon dioxide

SOG Spin-on-glass

SPM Scanning probe microscope

SR Spectral reflectance

Ta<sub>2</sub>O<sub>5</sub> Tantalum oxide

TAT Trap-assited tunneling

TFL Trap-filled limited

Ti Titanium

TIVA Thermally-induced voltage alteration

UV Ultraviolet

XRD X-ray diffraction

XRF X-ray fluorescent

Zn Zinc

# STRUKTUR PERANTI SEMIKONDUKTOR Al/Ta<sub>2</sub>O<sub>5</sub>/GaN

#### **ABSTRAK**

Peranti semikonduktor berasaskan GaN telah dikaji secara menyeluruh bagi penggunaan dalam kuasa dan suhu tinggi bagi menggantikan Si yang tidak dapat lagi memenuhi keperluan tersebut. Sifat seperti kebocoran arus yang rendah, ketumpatan cas oksida yang rendah, dan kapasitan yang tinggi amat diperlukan untuk peranti MOS berasaskan GaN berkualiti tinggi. Dalam pada itu, terdapat juga kecenderungan tinggi dalam membangunkan transistor MOS berasaskan GaN. Kajian pada awal tahun 2000-an menggunakan filem oksida GaN sebagai dielektrik di dalam struktur MOS. Pada hujung tahun 2000-an, MOS berasaskan GaN dengan dielektrik seperti Al<sub>2</sub>O<sub>3</sub>, MgO, Sc<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>, dan Ta<sub>2</sub>O<sub>5</sub> telah dibangunkan.

Dalam penyelidikan ini, wafer komersial yang mengandungi GaN-atas-nilam digunakan sebagai semikonduktor. Penebat pintu dibina dengan memendapkan bahan oksida terpilih seperti SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> dan Ta<sub>2</sub>O<sub>5</sub> ke atas GaN menggunakan teknik percikan frekuensi-radio. Logam pintu pula dibina dengan menyejatkan aluminum ke atas penebat. Pencirian bagi penebat dilakukan menerusi AFM, XRD, XRF, SEM dan EDX. Selain itu, pengukuran C-V, I-V dan D<sub>it</sub> dilakukan untuk menentukan ciri elektrik struktur MOS. Ciri asas struktur MOS dengan dielektrik SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> dan Ta<sub>2</sub>O<sub>5</sub> telah dikaji dan dibandingkan. Kajian ini disusuli dengan kes penyelidikan terhadap struktur MOS Al/Ta<sub>2</sub>O<sub>5</sub>/GaN yang merangkumi sepuhlindap selepas-pemendapan, sepuhlindap selepas-pelogaman, tegasan suhu substrat, tegasan voltan malar, dan tegasan sinaran cahaya.

Penyelidikan ini telah membuktikan bahawa struktur MOS yang difabrikasi dengan Ta<sub>2</sub>O<sub>5</sub> bernilai k tinggi mempunyai prestasi yang paling baik dari segi ketumpatan cas oksida yang rendah, ketumpatan perangkap antaramuka yang rendah, kapasitan yang tinggi, kekonduksian dinamik yang tinggi, kestabilan dalam operasi suhu tinggi, serta ketahanan dalam keadaan tegasan voltan malar. Ciri-ciri peranti yang diperoleh daripada penyelidikan ini adalah lebih baik jika dibandingkan dengan sesetengah data daripada literatur.

# $Al/Ta_2O_5/GaN$ SEMICONDUCTOR DEVICE STRUCTURE

#### **ABSTRACT**

GaN-based semiconductor devices have been extensively investigated for used in high power and high temperature device applications in order to replace Si which is no longer capable to fulfill these ever-increasing demands. The characteristics of low leakage current, low oxide charge density, and high oxide capacitance would be necessary for device-quality GaN-based MOS devices. Along this, there is a great interest in development of GaN-based MOS transistors. The foremost work in early 2000s used a thermally oxidized GaN film as the gate dielectric in MOS structure. In late 2000s, GaN-based MOS with other dielectrics such as Al<sub>2</sub>O<sub>3</sub>, MgO, Sc<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub> were developed.

In the present work, commercial GaN-on-sapphire wafer was used as the semiconductor. The gate insulator was obtained by depositing selected oxide materials of SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and Ta<sub>2</sub>O<sub>5</sub> onto GaN using RF-sputtering technique. The gate metal was built by evaporating aluminium onto the insulator. The deposited insulators were characterized using AFM, XRD, XRF, SEM, and EDX. On the other hand, C-V, I-V, and D<sub>it</sub> measurements were carried out to determine the electrical characteristics of the MOS structures. The fundamental properties of MOS structures with SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and Ta<sub>2</sub>O<sub>5</sub> gate dielectrics were studied and compared. Then, case studies of post-deposition annealing, post-metallization annealing, substrate temperature stress, constant voltage stress, and light radiation stress were investigated on the Al/Ta<sub>2</sub>O<sub>5</sub>/GaN MOS structure.

The research results revealed that MOS structure with high-k dielectric of  $Ta_2O_5$  possessed the best performance in term of lower oxide charge density, lower interface trap density, higher storage capacitance, higher dynamic conductivity, stability in high temperature operation, and durability in constant voltage stress. These characteristics were even better than the ones reported in some existing literatures.

#### CHAPTER 1

#### Literature Reviews

#### 1.1 Introduction

MOS (Metal-Oxide-Semiconductor) is the heart of MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) which forms the basic building block of charge-coupled device as storage capacitor in integrated circuits and memories. The first MOSFET was invented by Kahng and Atalla in 1960 using a thermally oxidized silicon (Si) substrate. The silicon dioxide (SiO<sub>2</sub>) thickness was 100 nm with gate length of 20 µm. Two keyholes were made on this device for drain and source contacts, while aluminium (Al) was evaporated onto the top elongated area for gate contact. Although today's device has been scaled down into deep submicron regime, Si is still dominating about 90% of the semiconductor devices market [1]. Marching into 21st century, semiconductor industry is seeing greater demand on higher power, high temperature, high voltage, improved spectra purity, and increased bandwidth, especially in the wireless communication technology. Nevertheless, Si is no longer capable to fulfill these ever-increasing demands. Of all design factors, power consumption is the most critical issue as it influences the device reliability significantly. To address this problem, researchers are currently focusing on new semiconductor materials used in power transistor and gallium nitride (GaN) has emerged as the true contender [2].

#### 1.2 Overview of GaN

#### 1.2.1 Crystal Structure

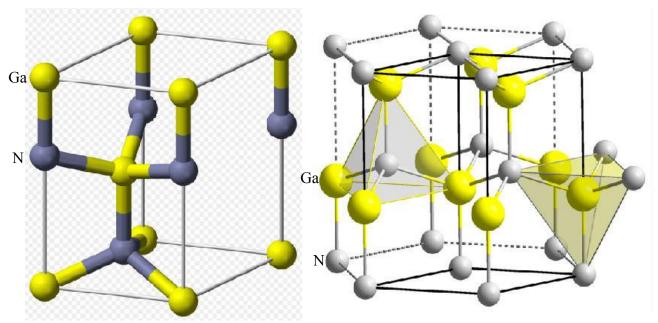

GaN is a hard and mechanically stable material with large heat capacity. It is a binary group III-group V direct band gap semiconductor of wurtzite crystal structure (Figure 1.1 & Figure 1.2). Each of the Ga atom and the N atom is tetrahedrally coordinated and each forms a sublattice which is hexagonal close-pack. The atomic positions are the same as in lonsdaleite (hexagonal diamond). The wurtzite structure is non-centrosymmetric (lacks inversion symmetry), thus it has properties such as piezoelectricity and pyroelectricity, which are not found in the centrosymmetric crystal [3].

Figure 1.1 Wurtzite unit cell [3]

Figure 1.2 Wurtzite structure [3]

#### **1.2.2 History**

In 1932, GaN was synthesized in powder form. In 1938, GaN was synthesized in small needles. In 1969, GaN was first grown on a sapphire substrate using hydride vapor phase epitaxy (HVPE). In 1971, GaN was grown epitaxially via metal-organic chemical vapor deposition (MOCVD) and by molecular beam epitaxy (MBE) in 1974. However, lattice mismatch led to poor quality of epitaxial layer until early 1980s. These early epilayers were always unintentionally doped n-type ( $n \ge 1 \times 10^{17} \text{ cm}^{-3}$ ), resulting from growth defects or impurities inadvertently introduced during the growth. In 1983, Yoshida et al. improved the epilayer quality by using a two-step growth method, where a thin AlN buffer layer was grown on the sapphire substrate. He managed to confine most mismatch-induced dislocations to a thin AlN/GaN interfacial region rather than throughout the GaN epilayer. In 1989, Amano et al. developed p-type GaN using low energy electron beam irradiation (LEEBI) of Mg-doped GaN. The energy provided by the electron beam depassivated the Mg acceptors by breaking the Mg—H bonds formed during MOCVD growth. Today's GaN epilayers are grown on either  $\beta$ -Al<sub>2</sub>O<sub>3</sub> sapphire or 6H-SiC substrate. The differences between the two are shown in Table 1.1 [4].

Table 1.1 Comparison of properties between β-Al<sub>2</sub>O<sub>3</sub> sapphire and 6H-SiC substrate [4]

| Property                            | β-Al <sub>2</sub> O <sub>3</sub> Sapphire | <b>6H-SiC Substrates</b>   |  |

|-------------------------------------|-------------------------------------------|----------------------------|--|

| Cost                                | Cheaper                                   | Expensive                  |  |

| Lattice mismatch to GaN             | 13%                                       | 3.5%                       |  |

| Thermal conductivity                | Lower                                     | 10x higher                 |  |

| Threading dislocation concentration | $2x10^9 \text{ cm}^{-2}$                  | $5x10^{8} \text{ cm}^{-2}$ |  |

#### 1.2.3 Synthesis

MOCVD, MBE, HVPE, and ELOG are four common techniques used for the growth of GaN. MOCVD is more popular for group III-nitride growth with an optimum growth temperature of 1050 °C and growth rate of 2 μm/hr for GaN. MBE process uses NH<sub>3</sub> as the nitrogen source at growth temperature of 900-1000 °C and growth rate of 1 μm/hour. HVPE has growth rate of 10 μm/hour and it provides lower dislocation density free-standing thick GaN layers after the substrate has been removed. During ELOG (epitaxial lateral overgrowth) of GaN, thin strips of SiO<sub>2</sub> are patterned on a GaN buffer layer. GaN growth continues selectively on the GaN buffer layer then laterally over the SiO<sub>2</sub> strips. When the SiO<sub>2</sub> mask has been overgrown, the GaN over the SiO<sub>2</sub> has a much lower dislocation density [4].

#### 1.2.4 Applications

GaN has been widely used in optoelectronic devices such as light emitting diode, laser diode, and solar cell for years. GaN can be doped with transition metal like manganese to form spintronics material (magnetic semiconductor). Nanotube of GaN is applied in nanoscale electronic and biochemical sensing application [3]. Nowadays, a wide variety of electronic devices are fabricated using GaN, including heterojunction bipolar transistors (HBTs), heterojunction field effect transistors (HFETs), and high electron mobility transistors (HEMTs). Recently, many researches are focusing on designing the state-of-the-art of microwave power transistors for wireless communication and GaN is emerging as the front runner compared to other semiconductor materials. This is owing to its unique material and electronic properties (Table 1.2) [4].

#### 1.2.5 Physical and Electrical Properties

GaN is a very hard but mechanically stable material with large heat capacity. The comparisons between GaN with other semiconductor materials are given in Table 1.2 [4].

Table 1.2 The properties of various semiconductor materials [4]

| Property                                              | C                    | GaAs                  | GaN InP                |                       | Si        | 4H-SiC                 |

|-------------------------------------------------------|----------------------|-----------------------|------------------------|-----------------------|-----------|------------------------|

| Band gap at 300 K (eV)                                | 5.47 (I)             | 1.424 (D)             | 3.44 (D)               | 1.344 (D)             | 1.12 (I)  | 3.26 (I)               |

| Dielectric constant                                   | 5.57 (dc)            | 13.2 (dc)<br>10.9 (∞) | 8.9 (dc)<br>5.35 (∞)   | 12.4 (dc)<br>9.66 (∞) | 11.7 (dc) | 9.6 (dc)<br>6.7 (∞)    |

| Thermal expansion (x10 <sup>-6</sup> K.∆a/a)          | 0.08                 | 6.86                  | 5.59                   | 4.5                   | 2.56      | 4.2                    |

| Lattice<br>constant (Å)                               | 3.567                | 5.653                 | 3.189 (a)<br>5.185 (c) | 5.869                 | 5.431     | 3.073 (a)<br>10.05 (c) |

| $m_n/m_o$                                             | 0.2                  | 0.063                 | 0.22                   | 0.077                 | 1.18      | -                      |

| $m_p/m_o$                                             | $m_0$ 0.25 0.53      |                       | 0.8                    | 0.64                  | 0.81      | -                      |

| Bulk<br>mobility<br>(cm <sup>2</sup> /Vs)<br>Electron | 2200                 | 8500                  | 900                    | 4600                  | 1450      | 1140                   |

| Hole 1600 400                                         |                      | 400                   | 150                    | 150                   | 500       | 50                     |

| Saturation velocity (x10 <sup>7</sup> cm/s)           | 2.7                  | 1.0                   | 2.5                    | -                     | 1.0       | 2.0                    |

| Breakdown<br>field<br>(MV/cm)                         | 10                   | 0.4                   | 5                      | -                     | 0.3       | 3                      |

| Thermal conductivity (W/cmK)                          | conductivity 22 0.46 |                       | 1.3                    | 0.68                  | 1.5       | 4.9                    |

| Melting<br>point (K)                                  | 3826                 | 1238                  | Sublimes T > 1300      | 1070                  | 1412      | Sublimes T > 1827      |

GaN has band gap energy of 3.4 eV at room temperature, enabling GaN-based device to be having peak internal electric field about 5 times higher than that of Si or GaAs-based devices. This in turn renders higher breakdown voltage, which is necessary for high power handling and high efficiency achievement. GaN has high electron velocity which can minimize the internal device delay. GaN device offers higher impedance, higher bandwidth, and easier input matching. GaN does possess superior linearity (the converse of distortion) that helps to avoid excessive spillover between adjacent channels in power amplifier, thus enable achievement of higher amplifier efficiency. Efficiency is referred to the ability of transistor and amplifier to convert electrical power into output power. On the other hand, GaN exhibits maximum output power density as high as 4 times than that of GaAs. This allows smaller chip to handle the same amount of power. In other words, more chips can be fabricated on a wafer, leading to reduction of cost per chip. Alternatively, the same size device can handle higher power, leading to lower cost per watt of power and thus lower system cost [2].

#### 1.2.6 Figure of Merit (FOM)